PCB接地层可以降低噪声?如何降低?图文结合,一文帮你全部搞定

PCB设计发布于 • 阅读量 989

百芯EMA-国内DFM可制造性分析工具:PCB/PCBA 3D仿真+BOM物料管理+PCB/PCBA DFM 可制造性分析

大家有没有想过,为什么在PCB设计中应尽可能使用接地层?接地层可以降低信号返回路径的电感,反过来又最大限度地减少瞬态接地电流的噪声。

在这里主要是关于信号路径在多层PCB上的工作原理以及返回路径电感。

一、信号选择阻抗最小的路径

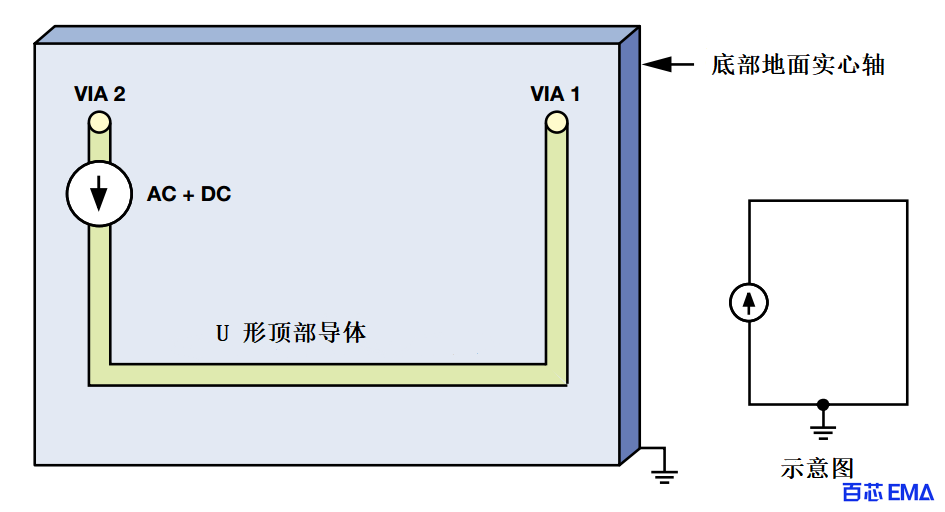

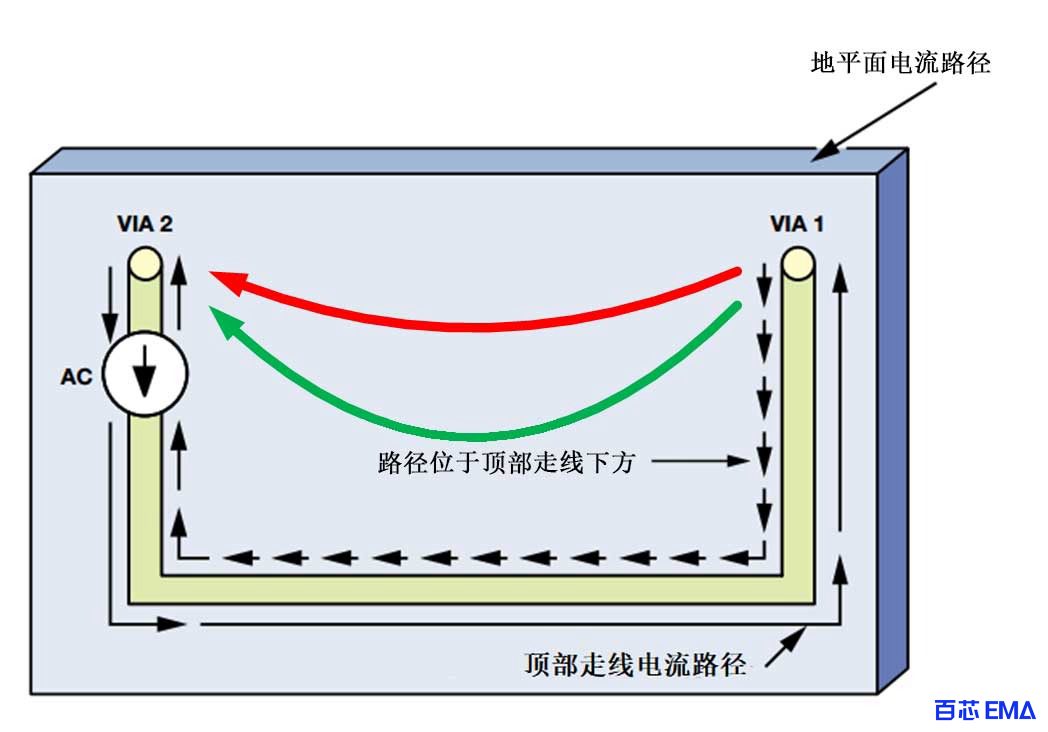

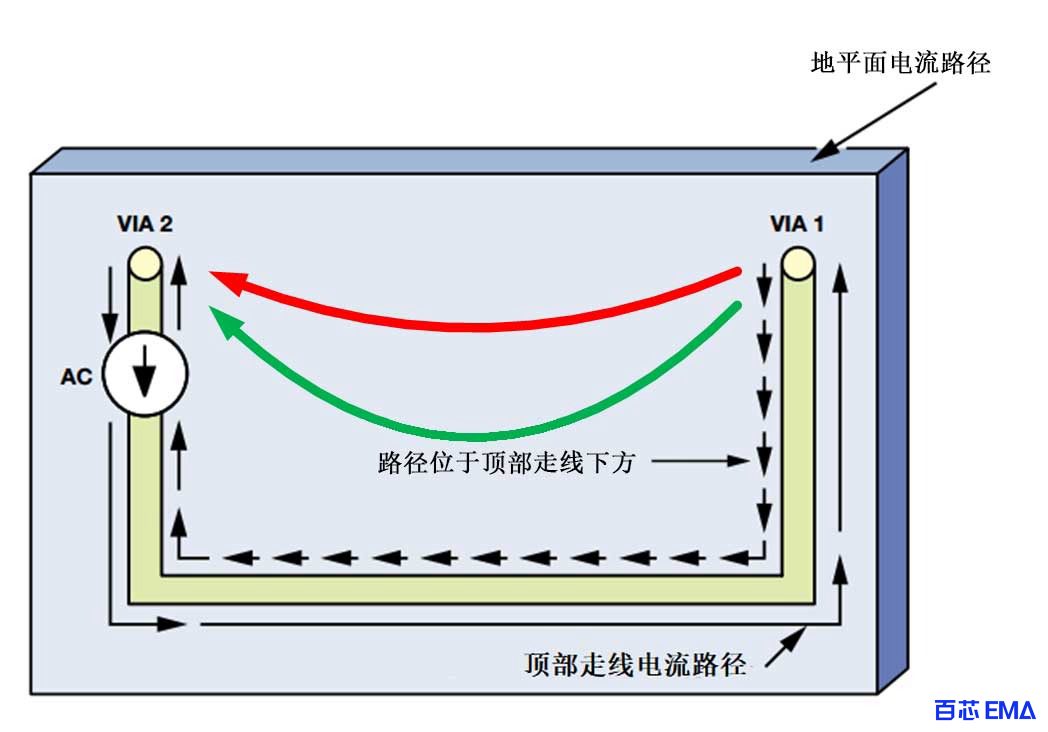

考虑如下图所示的双层板。底层是接地层,电流源连接到顶层的U形走线。顶层走线通过 VIA1 和 VIA2 连接到底层。

顶层走线通过 VIA1 和 VIA2 连接到底层

首先,如下图所示,将直流电流注入顶层走线。

将直流电流注入顶层走线

电流沿着U型走线流动,然后,通过VIA到达地面。接地层的哪一部分会将电流传导回VIA2?

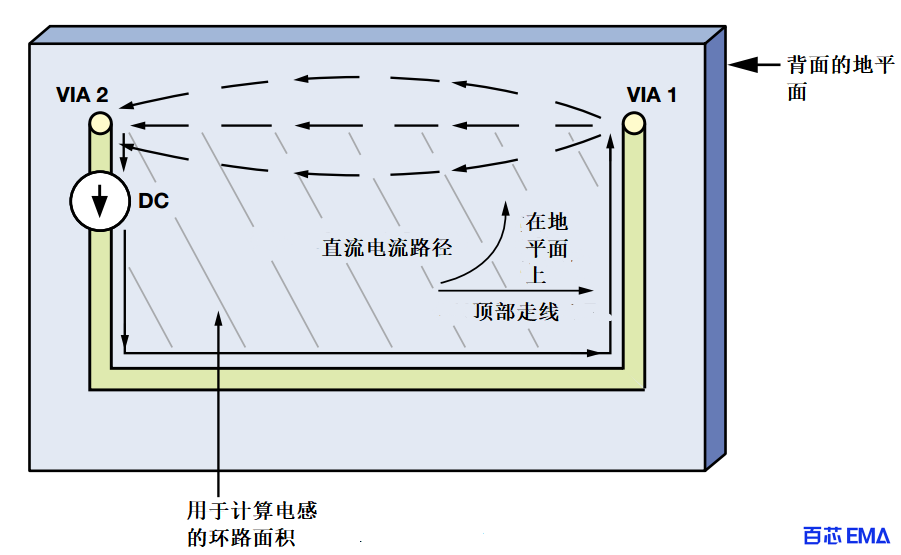

这里我们可以将地平面想象为无数条平行的窄走线。电流将选择表现出相对较小的走线。由于从VIA1到VIA2的直接路径最短且电阻最小,因此大部分电流将流经该路径。当我们远离这条阻力最小的路径时,电流密度将迅速下降。

现在,假设我们将交流电流注入U形走线。会采取与直流电流相容的路径吗?

直流电流采用阻抗最小(或电阻最小)的路径。对于交流电流,阻抗取决于路径的电阻和电感,虽然最短路径提供最小的电阻,但不一定提供最小的电感。

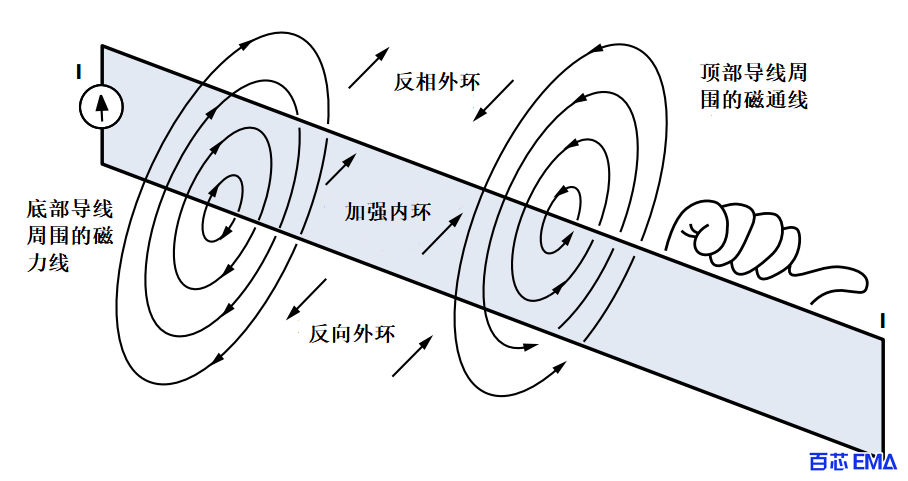

路径的电感取决于电流产生的环路面积。下图显示了信号走线及其返回路径创建的示例电流环路。如果电流形成的回路面积增加,则电感将比例增加。

信号走线及其返回路径创建的示例电流环路。

例如,下图中的红色返回路径创建的环路比绿色路径更大。因此,在这2条路径之间,交流电流通过绿色路径,该路径具有较小的电感。

对于路径的整体阻抗,我们实际上应该考虑电阻和电感。然而随着交流信号频率的增加。电感对路径阻抗的贡献最终会比电阻大几个数量级。

因此,如下图所示,高频返回电流将直接在U形走线下方流动,以最大限度地减少环路面积(这里忽略路径电路)

当我们远离接地层中的这条路径时,电流密度将迅速下降。

高频返回电流将直接在U形走线下方流动

二、为什么返回路径电感很重要?

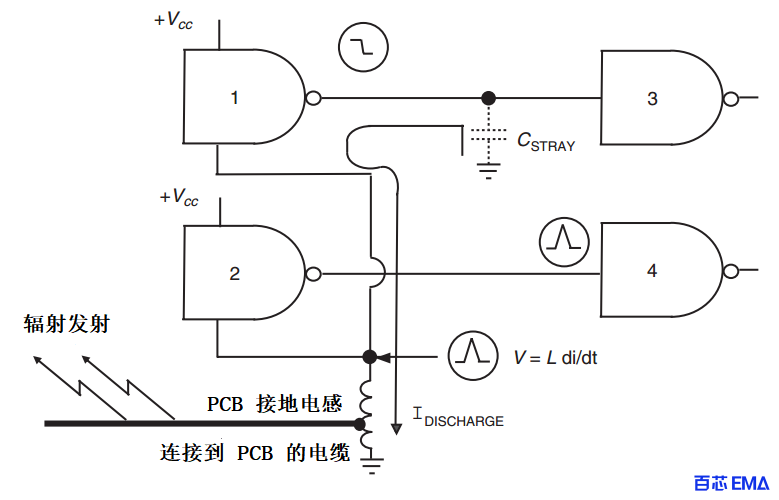

通过将电感与电路原理图的接地串联,可以获得返回路径电感的简单模型。下图显示了一个示例,假设门1的输出从逻辑高电平变为逻辑低电平。

将通过接地路径释放C中存储的电荷,考虑到快速逻辑门,放电将在很短的时间内(Δt)发生,放电电流将流过接地电感,如果在逻辑转换期间流过电感的电流变换Δ I,则逻辑门的接地将反弹。

在这种情况下,处于逻辑低电平的门(图 4 中的门 2)的输出将经历噪声电压脉冲。如果足够大,该噪声电压可能会导致门 4 输出处出现不需要的转换。

此外,如下图所示,接地噪声电压可能会耦合到离开 PCB 的电缆。这些电缆充当天线,会辐射并导致 EMC 问题。

高频返回电流将直接在U形走线下方流动

在下图中,揭示了接地电感可能导致问题的另一个机制。当门1的输出从逻辑高电平准换为逻辑低电平时,门1内部的晶体管将杂散电容连接到由接地路径创建的电感。

如果将电容连接到接地电感的晶体管表现出较小的电阻,则会创建高Q至串联谐振电路。可能会导致逻辑门转换产生相当大的振铃,如果我们不能充分降低接地电感,可能需要添加一个与栅极输出串联的电阻(例如51Ω)以一直振铃。

接地电感可能导致问题的另一个机制

上面噪声机制表明,在设计PCB时,接地路径电感至关重要。

如前所述,多层板需要坚固的接地层,可以显著降低接地电感。但是对于双面板,我们必须采取其他技术来实现低电感接地系统。

以上就是关于PCB接地层如何降低噪声的知识。

关于PCB 接地的更多内容,欢迎阅读以下文章: