Datasheet 搜索 > 计数器 > Toshiba(东芝) > TC74VHC4040FN 数据手册 > TC74VHC4040FN 其他数据使用手册 1/11 页

器件3D模型

器件3D模型¥ 0.311

TC74VHC4040FN 其他数据使用手册 - Toshiba(东芝)

制造商:

Toshiba(东芝)

分类:

计数器

封装:

SOP

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

TC74VHC4040FN数据手册

Page:

of 11 Go

若手册格式错乱,请下载阅览PDF原文件

TC74VHC4040F/FN/FT/FK

2007-10-01

1

TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

TC74VHC4040F,TC74VHC4040FN,TC74VHC4040FT,TC74VHC4040FK

12-Stage Ripple Carry Binary Counter

The TC74VHC4040 is an advanced high speed CMOS

12-STAGE BINARY COUNTER/DIVIDER fabricated with silicon

gate C

2

MOS technology.

It achieves the high speed operation similar to equivalent

Bipolar Schottky TTL while maintaining the CMOS low power

dissipation.

Setting CLR to high resets the counter to low.

A negative transition on the

CK

input brings one increment

into the counter.

This counter provides all divided output stages, and at Q12, a

1/4096 divided frequency will be output.

An input protection circuit ensures that 0 to 5.5 V can be

applied to the input pins without regard to the supply voltage.

This device can be used to interface 5 V to 3 V systems and two

supply systems such as battery back up. This circuit prevents

device destruction due to mismatched supply and input voltages.

Features

• High speed: f

max

= 210 MHz (typ.) at V

CC

= 5 V

• Low power dissipation: I

CC

= 4 μA (max) at Ta = 25°C

• High noise immunity: V

NIH

= V

NIL

= 28% V

CC

(min)

• Power down protection is provided on all inputs.

• Balanced propagation delays: t

pLH

∼

−

t

pHL

• Wide operating voltage range: V

CC (opr)

= 2 V to 5.5 V

• Low noise: V

OLP

= 1.5 V (max)

• Pin and function compatible with 74HC4040

Weight

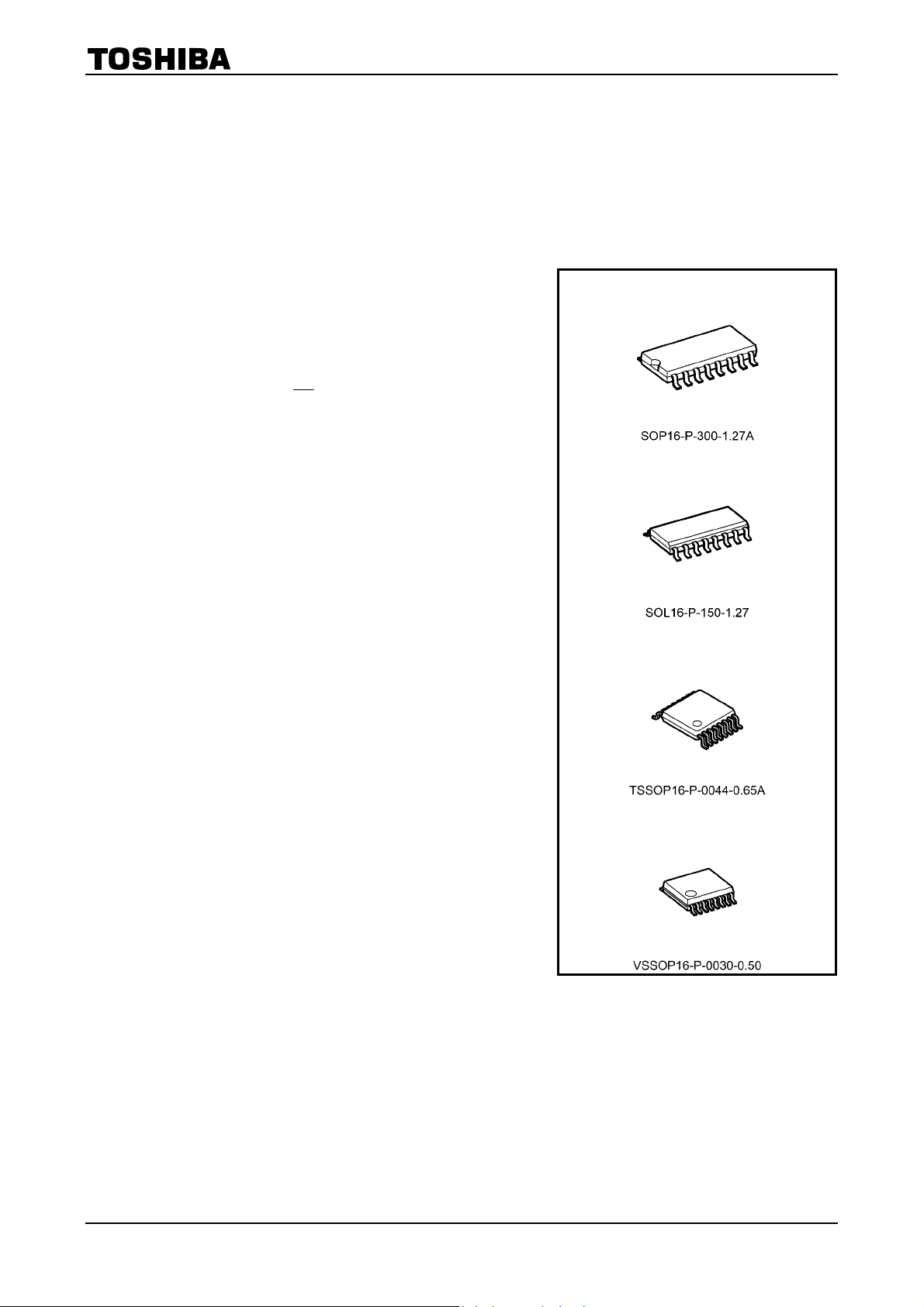

SOP16-P-300-1.27A : 0.18 g (typ.)

SOL16-P-150-1.27 : 0.13 g (typ.)

TSSOP16-P-0044-0.65A : 0.06 g (typ.)

VSSOP16-P-0030-0.50 : 0.02 g (typ.)

Note: xxxFN (JEDEC SOP) is not available in

Japan.

TC74VHC4040F

TC74VHC4040FN

TC74VHC4040FT

TC74VHC4040FK

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件