Datasheet 搜索 > 振荡器 > Silicon Labs(芯科) > 510BBA100M000BAG 数据手册 > 510BBA100M000BAG 数据手册 1/26 页

¥ 7.939

510BBA100M000BAG 数据手册 - Silicon Labs(芯科)

制造商:

Silicon Labs(芯科)

分类:

振荡器

封装:

SMD-6

描述:

SILICON LABS 510BBA100M000BAG 振荡器, 100MHZ, ±50PPM, 3.3V, SMD

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P1P12Hot

典型应用电路图在P26

原理图在P1

封装尺寸在P10P16P18P20P22

型号编码规则在P1P14

封装信息在P14

技术参数、封装参数在P4P11P24

应用领域在P1

电气规格在P4

型号编号列表在P24

导航目录

510BBA100M000BAG数据手册

Page:

of 26 Go

若手册格式错乱,请下载阅览PDF原文件

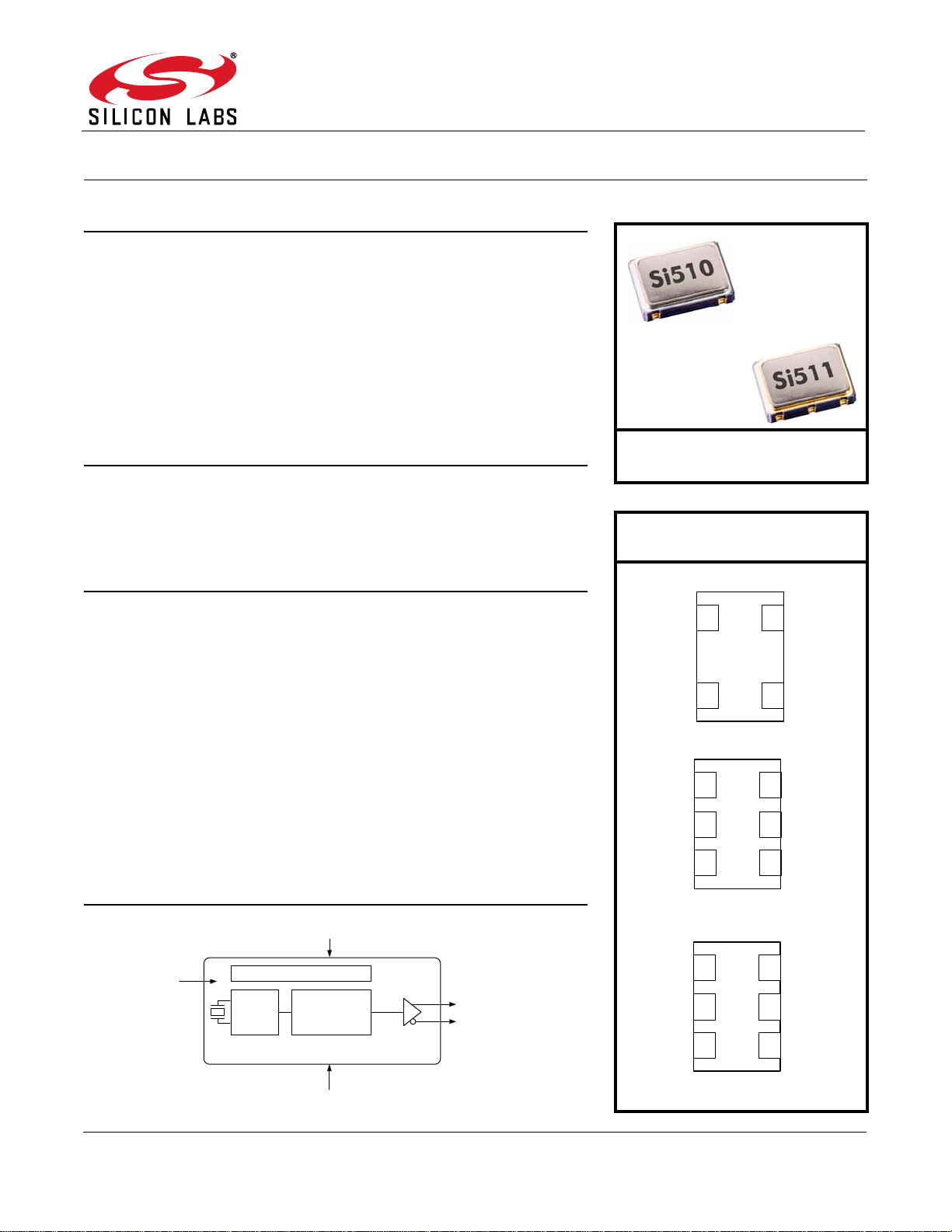

Rev. 1.2 7/15 Copyright © 2015 by Silicon Laboratories Si510/511

Si510/511

CRYSTAL OSCILLATOR (XO) 100 kHZ TO 250 MHZ

Features

Applications

Description

The Si510/511 XO utilizes Silicon Laboratories' advanced DSPLL technology

to provide any frequency from 100 kHz to 250 MHz. Unlike a traditional XO

where a different crystal is required for each output frequency, the Si510/511

uses one fixed crystal and Silicon Labs’ proprietary DSPLL synthesizer to

generate any frequency across this range. This IC-based approach allows

the crystal resonator to provide enhanced reliability, improved mechanical

robustness, and excellent stability. In addition, this solution provides superior

supply noise rejection, simplifying low jitter clock generation in noisy

environments. Crystal ESR and DLD are individually production-tested to

guarantee performance and enhance reliability. The Si510/511 is factory-

configurable for a wide variety of user specifications, including frequency,

supply voltage, output format, output enable polarity, and stability. Specific

configurations are factory-programmed at time of shipment, eliminating long

lead times and non-recurring engineering charges associated with custom

frequency oscillators.

Functional Block Diagram

Supports any frequency from

100 kHz to 250 MHz

Low jitter operation

2 to 4 week lead times

Total stability includes 10-year

aging

Comprehensive production test

coverage includes crystal ESR and

DLD

On-chip LDO regulator for power

supply noise filtering

3.3, 2.5, or 1.8 V operation

Differential (LVPECL, LVDS,

HCSL) or CMOS output options

Optional integrated 1:2 CMOS

fanout buffer

Runt suppression on OE and

power on

Industry standard 5 x 7 and

3.2x5 mm packages

Pb-free, RoHS compliant

–40 to 85

o

C operation

SONET/SDH/OTN

Gigabit Ethernet

Fibre Channel/SAS/SATA

PCI Express

3G-SDI/HD-SDI/SDI

Telec o m

Switches/routers

FPGA/ASIC clock generation

V

DD

Any-Frequency

0.1 to 250 MHz

DSPLL

®

Synthesis

Fixed

Frequency

Oscillator

CLK+

CLK–

OE

GND

Low Noise Regulator

Ordering Information:

See page 14.

Pin Assignments:

See page 12.

Si5602

1

2

3

6

5

4GND

OE

V

DD

CLK+

CLK–

NC

1

2

3

6

5

4GND

NC

V

DD

CLK+

CLK–

OE

Si510(LVDS/LVPECL/HCSL/

Dual CMOS)

Si510 (CMOS)

Si511(LVDS/LVPECL/HCSL/

Dual CMOS)

1

2

4

3GND

V

DD

CLK

OE

1

2

3

6

5

4GND

NC

V

DD

CLK+

CLK–

OE

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件