Datasheet 搜索 > FPGA芯片 > Altera(阿尔特拉) > 5CGXFC5F7M11C8N 数据手册 > 5CGXFC5F7M11C8N 数据手册 13/41 页

¥ 870.862

5CGXFC5F7M11C8N 数据手册 - Altera(阿尔特拉)

制造商:

Altera(阿尔特拉)

分类:

FPGA芯片

封装:

MBGA-301

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P33Hot

典型应用电路图在P5P7P9P13P15P17

型号编码规则在P5P7P9P12P14P16

封装信息在P2

导航目录

5CGXFC5F7M11C8N数据手册

Page:

of 41 Go

若手册格式错乱,请下载阅览PDF原文件

Maximum Resources

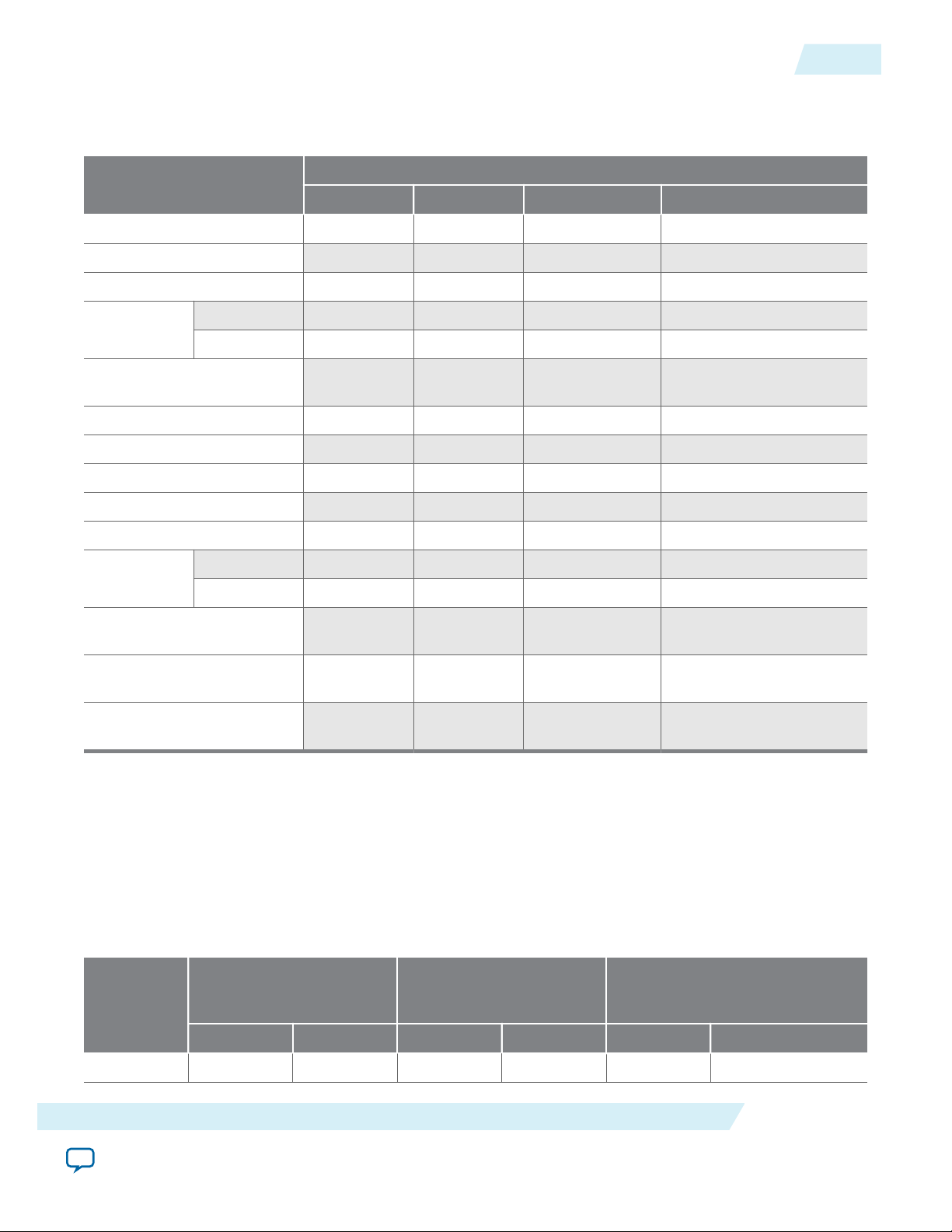

Table 10: Maximum Resource Counts for Cyclone V SE Devices

Resource

Member Code

A2 A4 A5 A6

Logic Elements (LE) (K) 25 40 85 110

ALM 9,434 15,094 32,075 41,509

Register 37,736 60,376 128,300 166,036

Memory

(Kb)

M10K 1,400 2,700 3,970 5,570

MLAB 138 231 480 621

Variable-precision DSP

Block

36 84 87 112

18 x 18 Multiplier 72 168 174 224

FPGA PLL 5 5 6 6

HPS PLL 3 3 3 3

FPGA GPIO 145 145 288 288

HPS I/O 181 181 181 181

LVDS

Transmitter 32 32 72 72

Receiver 37 37 72 72

FPGA Hard Memory

Controller

1 1 1 1

HPS Hard Memory

Controller

1 1 1 1

ARM Cortex-A9 MPCore

Processor

Single- or

dual-core

Single- or

dual-core

Single- or dual-

core

Single- or dual-core

Related Information

True LVDS Buffers in Devices, I/O Features in Cyclone V Devices

Provides the number of LVDS channels in each device package.

Package Plan

Table 11: Package Plan for Cyclone V SE Devices

The HPS I/O counts are the number of I/Os in the HPS and does not correlate with the number of HPS-specific

I/O pins in the FPGA. Each HPS-specific pin in the FPGA may be mapped to several HPS I/Os.

Member

Code

U484

(19 mm)

U672

(23 mm)

F896

(31 mm)

FPGA GPIO HPS I/O FPGA GPIO HPS I/O FPGA GPIO HPS I/O

A2 66 151 145 181 — —

CV-51001

2016.06.10

Maximum Resources

13

Cyclone V Device Overview

Altera Corporation

Send Feedback

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件