Datasheet 搜索 > 逻辑芯片 > Fairchild(飞兆/仙童) > 74AC08SJ 数据手册 > 74AC08SJ 数据手册 6/10 页

器件3D模型

器件3D模型¥ 0.472

74AC08SJ 数据手册 - Fairchild(飞兆/仙童)

制造商:

Fairchild(飞兆/仙童)

分类:

逻辑芯片

封装:

SOIC-14

描述:

四2输入与门 Quad 2-Input AND Gate

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

74AC08SJ数据手册

Page:

of 10 Go

若手册格式错乱,请下载阅览PDF原文件

©1988 Fairchild Semiconductor Corporation www.fairchildsemi.com

74AC08, 74ACT08 Rev. 1.5.1 6

74AC08, 74ACT08 — Quad 2-Input AND Gate

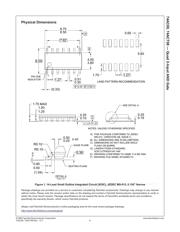

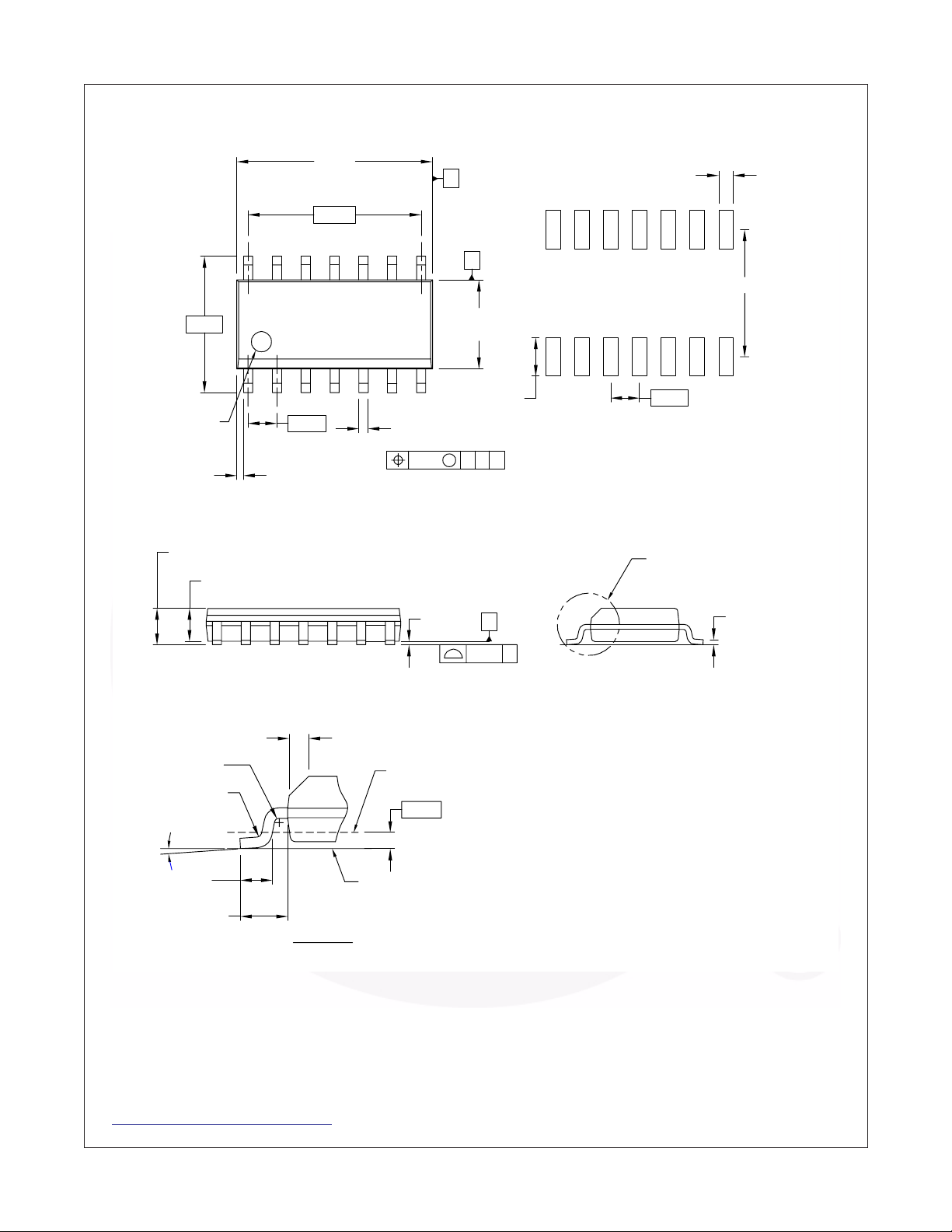

Physical Dimensions

Figure 1. 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or

obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions,

specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings:

http://www

.fairchildsemi.com/packaging/

LAND PATTERN RECOMMENDATION

NOTES: UNLESS OTHERWISE SPECIFIED

A) THIS PACKAGE CONFORMS TO JEDEC

MS-012, VARIATION AB, ISSUE C,

B) ALL DIMENSIONS ARE IN MILLIMETERS.

C) DIMENSIONS DO NOT INCLUDE MOLD

FLASH OR BURRS.

D) LANDPATTERN STANDARD:

SOIC127P600X145-14M

E) DRAWING CONFORMS TO ASME Y14.5M-1994

F) DRAWING FILE NAME: M14AREV13

PIN ONE

INDICATOR

8°

0°

SEATING PLANE

DETAIL A

SCALE: 20:1

GAGE PLANE

0.25

X45°

1

0.10

C

C

BC A

7

M

14

B

A

8

SEE DETAIL A

5.60

0.65

1.70 1.27

8.75

8.50

7.62

6.00

4.00

3.80

(0.33)

1.27

0.51

0.35

1.75 MAX

1.50

1.25

0.25

0.10

0.25

0.19

(1.04)

0.90

0.50

0.36

R0.10

R0.10

0.50

0.25

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件