Datasheet 搜索 > 触发器 > NXP(恩智浦) > 74HC123D 数据手册 > 74HC123D 数据手册 1/25 页

器件3D模型

器件3D模型¥ 7.295

74HC123D 数据手册 - NXP(恩智浦)

制造商:

NXP(恩智浦)

分类:

触发器

封装:

SOIC-16

描述:

NXP 74HC123D 逻辑芯片, CMOS, SMD, 74HC123, SOIC16

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

74HC123D数据手册

Page:

of 25 Go

若手册格式错乱,请下载阅览PDF原文件

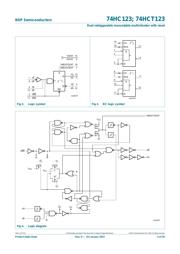

1. General description

The 74HC123; 74HCT123 are high-speed Si-gate CMOS devices and are pin compatible

with Low-power Schottky TTL (LSTTL). They are specified in compliance with JEDEC

standard no. 7A.

The 74HC123; 74HCT123 are dual retriggerable monostable multivibrators with output

pulse width control by three methods:

1. The basic pulse is programmed by selection of an external resistor (R

EXT

) and

capacitor (C

EXT

).

2. Once triggered, the basic output pulse width may be extended by retriggering the

gated active LOW-going edge input (nA

) or the active HIGH-going edge input (nB). By

repeating this process, the output pulse period (nQ = HIGH, nQ

= LOW) can be made

as long as desired. Alternatively an output delay can be terminated at any time by a

LOW-going edge on input nRD

, which also inhibits the triggering.

3. An internal connection from nRD

to the input gates makes it possible to trigger the

circuit by a HIGH-going signal at input nRD

as shown in Table 3.

Schmitt-trigger action in the nA

and nB inputs, makes the circuit highly tolerant to slower

input rise and fall times.

The 74HC123; 74HCT123 are identical to the 74HC423; 74HCT423 but can be triggered

via the reset input.

2. Features and benefits

DC triggered from active HIGH or active LOW inputs

Retriggerable for very long pulses up to 100 % duty factor

Direct reset terminates output pulse

Schmitt-trigger action on all inputs except for the reset input

ESD protection:

HBM JESD22-A114F exceeds 2000 V

MM JESD22-A115-A exceeds 200 V

Specified from 40 Cto+85C and from 40 Cto+125C

74HC123; 74HCT123

Dual retriggerable monostable multivibrator with reset

Rev. 9 — 19 January 2015 Product data sheet

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件