Datasheet 搜索 > 逻辑控制器 > NXP(恩智浦) > 74LVC161D,112 数据手册 > 74LVC161D,112 数据手册 1/22 页

器件3D模型

器件3D模型¥ 2.252

74LVC161D,112 数据手册 - NXP(恩智浦)

制造商:

NXP(恩智浦)

分类:

逻辑控制器

封装:

SOIC-16

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

74LVC161D,112数据手册

Page:

of 22 Go

若手册格式错乱,请下载阅览PDF原文件

1. General description

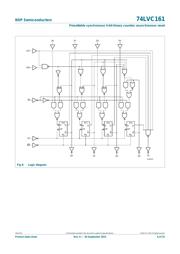

The 74LVC161 is a synchronous presettable binary counter which features an internal

look-ahead carry and can be used for high-speed counting. Synchronous operation is

provided by having all flip-flops clocked simultaneously on the positive-going edge of the

clock (pin CP). The outputs (pins Q0 to Q3) of the counters may be preset to a HIGH-level

or LOW-level. A LOW-level at the parallel enable input (pin PE

) disables the counting

action and causes the data at the data inputs (pins D0 to D3) to be loaded into the counter

on the positive-going edge of the clock (provided that the set-up and hold time

requirements for PE are met). Preset takes place regardless of the levels at count enable

inputs (pins CEP and CET). A LOW-level at the master reset input (pin MR

) sets all four

outputs of the flip-flops (pins Q0 to Q3) to LOW-level regardless of the levels at input pins

CP, PE

, CET and CEP (thus providing an asynchronous clear function).

The look-ahead carry simplifies serial cascading of the counters. Both count enable inputs

(pin CEP and CET) must be HIGH to count. The CET input is fed forward to enable the

terminal count output (pin TC). The TC output thus enabled will produce a HIGH output

pulse of a duration approximately equal to a HIGH-level output of Q0. This pulse can be

used to enable the next cascaded stage.

The maximum clock frequency for the cascaded counters is determined by t

PHL

(propagation delay CP to TC) and t

su

(set-up time CEP to CP) according to the formula:

It is a high-performance, low-power, low-voltage, Si-gate CMOS device and superior to

most advanced CMOS compatible TTL families.

2. Features and benefits

5 V tolerant inputs for interfacing with 5 V logic

Wide supply voltage range from 1.2 V to 3.6 V

CMOS low power consumption

Direct interface with TTL levels

Asynchronous reset

Synchronous counting and loading

Two count enable inputs for n-bit cascading

Positive edge-triggered clock

Complies with JEDEC standard:

JESD8-7A (1.65 V to 1.95 V)

JESD8-5A (2.3 V to 2.7 V)

74LVC161

Presettable synchronous 4-bit binary counter; asynchronous

reset

Rev. 6 — 30 September 2013 Product data sheet

f

max

1

t

PHL max

t

su

+

-----------------------------------

=

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件