Datasheet 搜索 > ADI(亚德诺) > AD9106 数据手册 > AD9106 数据手册 4/48 页

¥ 0

AD9106 数据手册 - ADI(亚德诺)

制造商:

ADI(亚德诺)

描述:

四,低功耗, 12位, 180 MSPS ,数位类比转换器和波形发生器 Quad, Low Power, 12-Bit, 180 MSPS, Digital-to-Analog Converter and Waveform Generator

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

AD9106数据手册

Page:

of 48 Go

若手册格式错乱,请下载阅览PDF原文件

AD9106 Data Sheet

Rev. A | Page 4 of 48

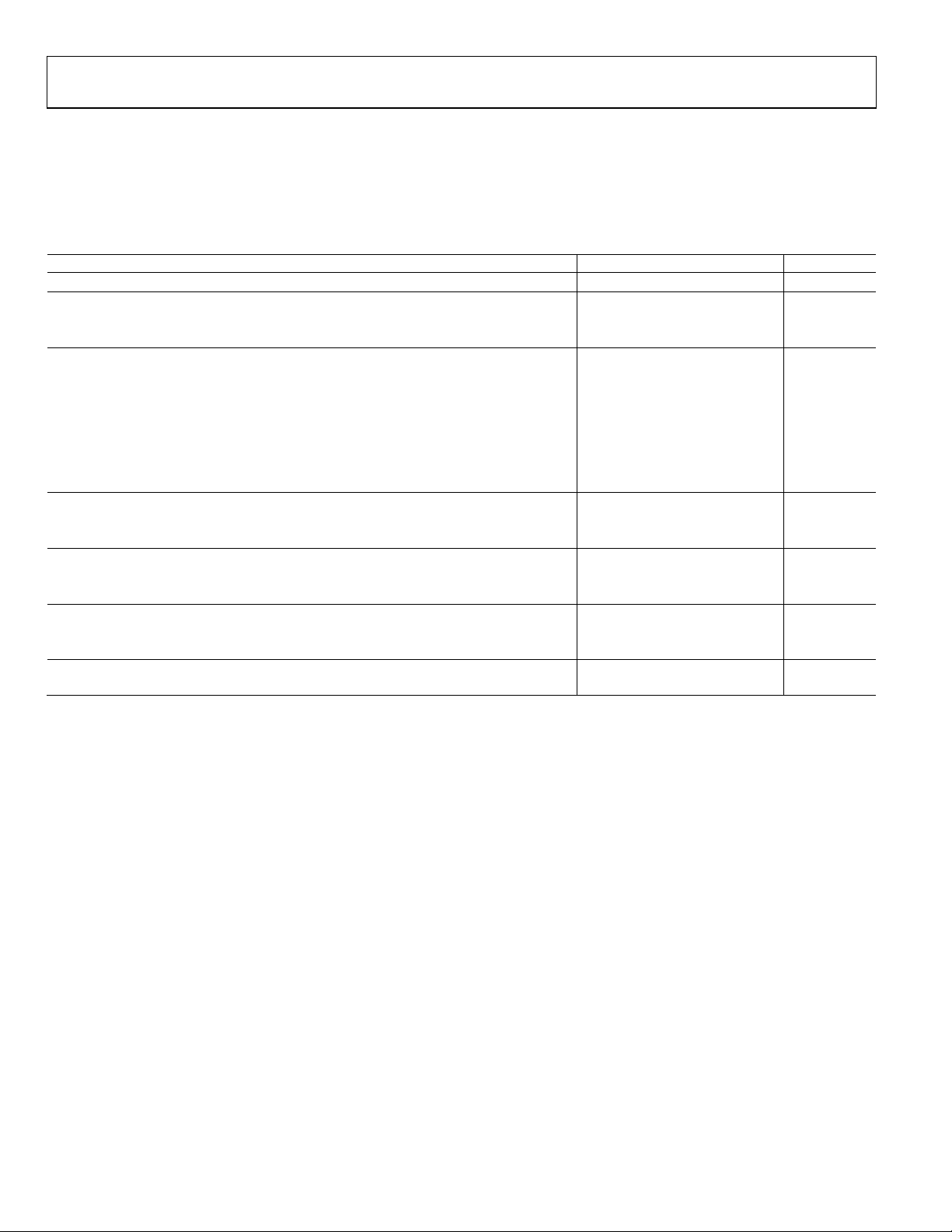

SPECIFICATIONS

DC SPECIFICATIONS (3.3 V)

T

MIN

to T

MAX

, AVDD = 3.3 V, DVDD = 3.3 V, CLKVDD = 3.3 V; internal CLDO, DLDO1, and DLDO2; I

OUTFS

= 4 mA, maximum sample rate,

unless otherwise noted.

Table 1.

Parameter Min Typ Max Unit

RESOLUTION 12 Bits

ACCURACY at 3.3 V

Differential Nonlinearity (DNL) ±0.4 LSB

Integral Nonlinearity (INL) ±0.5 LSB

DAC OUTPUTS

Offset Error ±.00025 % of FSR

Gain Error Internal Reference—No Automatic I

OUTFS

Calibration −1.0 +1.0 % of FSR

Full-Scale Output Current

1

at 3.3 V 2 4 8 mA

Output Resistance 200 MΩ

Output Compliance Voltage −0.5 +1.0 V

Crosstalk, DAC to DAC (f

OUT

= 10 MHz) 96 dBC

Crosstalk, DAC to DAC (f

OUT

= 60 MHz) 82 dBc

DAC TEMPERATURE DRIFT

Gain with Internal Reference ±251 ppm/°C

Internal Reference Voltage ±119 ppm/°C

REFERENCE OUTPUT

Internal Reference Voltage with AVDD = 3.3 V 0.8 1.0 1.2 V

Output Resistance 10 kΩ

REFERENCE INPUT

Voltage Compliance 0.1 1.25 V

Input Resistance External, Reference Mode 1 MΩ

DAC MATCHING

Gain Matching—No Automatic I

OUTFS

Calibration ±0.75 % of FSR

1

Based on use of 8 kΩ external xR

SET

resistors.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件