Datasheet 搜索 > ADI(亚德诺) > AD9271-50EBZ 数据手册 > AD9271-50EBZ 数据手册 47/58 页

¥ 0

AD9271-50EBZ 数据手册 - ADI(亚德诺)

制造商:

ADI(亚德诺)

描述:

八通道LNA / VGA / AAF / ADC与交叉点开关 Octal LNA/VGA/AAF/ADC and Crosspoint Switch

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P12P26Hot

原理图在P1P20P21P26P27P44P45P46P47P48

封装尺寸在P56

型号编码规则在P56

封装信息在P56

功能描述在P1P12

技术参数、封装参数在P1P3P4P5P6P7P8P9P10P11P12P13

应用领域在P1

电气规格在P17

导航目录

AD9271-50EBZ数据手册

Page:

of 58 Go

若手册格式错乱,请下载阅览PDF原文件

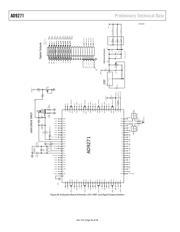

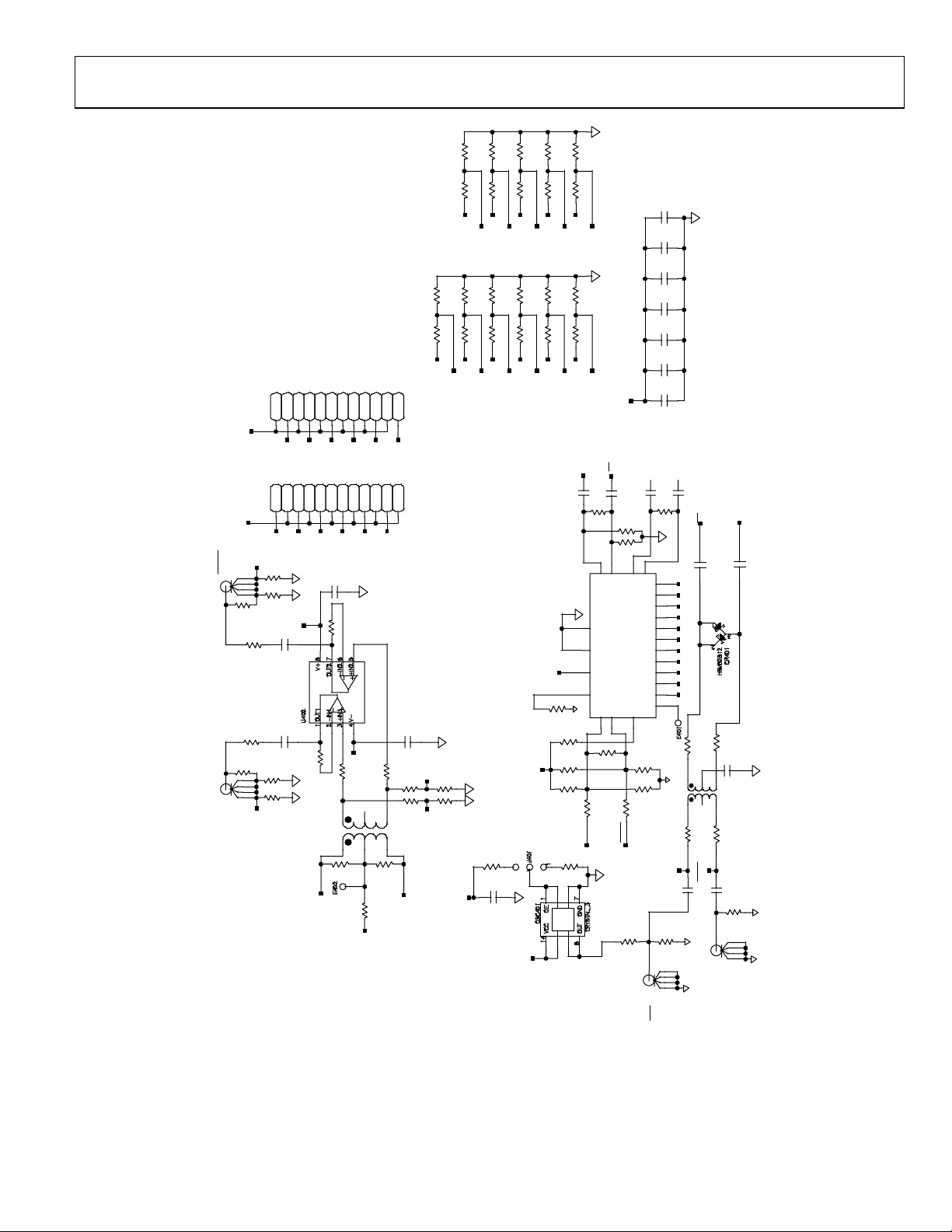

Preliminary Technical Data AD9271

Rev. PrA | Page 47 of 58

CLK

CLKB

GND

GND_PAD

OUT0

OUT0B

OUT1

OUT1B

RSET

S0

S1

S10

S2

S3

S4

S5

S6

S7

S8

S9

SYNCB

VREF

VS

SIGNAL=DNC;27,28

OE

GNDOUT

VCC

CW DOPPLER CIRCUITRY

DNP

DNP

DNP

DNP

DNP

Inpu t

Encod e

Enc

Enc

Clock Circuit

DNP

DNP

DNP

DNP

DNP

Optional Clock

Oscillator

AD9515 Pin-strap setting s

OPTIONAL CLOCK DRIVE CIRCUIT

CLIPSINEOUT (DEFAULT)

DNP

LVPECLOUTPUT

LVDS OUTPUT

AOUT

AOUT

ENABLE OS C201

DISABLEOSC201

DN P

0-DN P

R46 2R46 0

0-DN P

-5V

CWD2CWD1

CWD2

R46 4

0-DN P

0-DN P

R45 9 R46 1

0-DN P

0-DN P

R44 9 R46 6

0-DN P

AD812AR

R45 0

0

C40 3

0.1UF

0.1UF

C40 2

OPT_CLK

P402

10

12

3

5

OPT_CLK

50-D N P

R41 1

+5V

3

52

41

6

ADT1-1WT

T401

0

R40 3

R42 2

100

C419

0.1UF

C40 5

0.1U F- DN P

10 K

R41 3

12

6

7

25

8

16

9

15

10

14

11

13

3

2

5

18

19

23

22

32

1

31

33

U401

SIGNAL=AVDD_3.3V;4,17,20,21,24,26,29,30

AD9515

R40 9

DN P

R41 4

4.12 K

DN P

R40 8

0.1UF

C422

0

R424

R425

0

P401

J403J402

43

61

25

T402

ADTT 4-1

C411

0.1UF

R42 1

240

50

R40 4

R40 5

0

0.1UF

C421

R45 4

750

750

R45 3

ION

125

R44 7

R44 8

125

IOP

R45 2

0

0-DNP

R406

R407

0-DNP

R41 2

DN P

R40 1

10 K

C413

0.1UF

0

R416

0

R41 5

R417

0

R418

0

0.1UF- DN P

C40 7

0.1UF- DN P

C40 6

R45 1

0

AVDD_3.3V

0

R44 6

CLK

C409

0.1UF

C410

0.1UF

CLK

0.1UF

C420

C401

0.1UF

12

11

10

9

8

7

6

5

4

3

2

1

P403

1

2

3

4

5

6

7

8

9

10

11

12

P404

1

3

R427

00

R426

S0

0

R436

R437

0

0.1UF

C412 C415

0.1UF 0.1UF

C416

10 K

R40 2

0

R434

C40 8

0.1U F- DN P

R444

0

0

R442

R440

0

0

R438

R432

0

0

R430

R428

0

0

R445

R443

0

0

R441

R439

0

R435

0

0

R433

R431

0

0

R429

S4

S5

S3

S2

S1

AVDD_3 .3V

240

R42 0

R41 0

10 K

100

R42 3

AVDD_3 .3V

AVDD_3 .3V

AVDD_3 .3V

AVDD_3 .3V

AVDD_3. 3V AVDD_3.3V

AVDD_3.3V

AVDD_3.3V

AVDD_3.3V

AVDD_3.3V

S6

S7

S8

S9

S10

0.1UF

C414 C418

0.1UF0.1UF

C417

AVDD_3.3V

AVDD_3.3 V

AVDD_3. 3V

CLK

CLK

AVDD_3. 3V

OPT_CLK

OPT_CLK

S10S9 S8S7S6S5 S4S3S2S1S0

AVDD_3.3V

1

CWD5-

CWD3-

CWD2-

CWD1-

CWD0-

ION

CWD4-

CWD5+

CWD3+

CWD1+

CWD0+

CWD2+

IOP

CWD4+

0

R46 5

50

R45 5

50

R45 8

0-DN P

R46 3

CWD1

06304-089

Figure 70. Evaluation Board Schematic, Clock and CW Doppler Circuitry

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件