Datasheet 搜索 > ADI(亚德诺) > AD9972 数据手册 > AD9972 数据手册 1/2 页

¥ 0

AD9972 数据手册 - ADI(亚德诺)

制造商:

ADI(亚德诺)

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

原理图在P1

功能描述在P1

技术参数、封装参数在P1

应用领域在P1

导航目录

AD9972数据手册

Page:

of 2 Go

若手册格式错乱,请下载阅览PDF原文件

Dual-Channel, 14-Bit, CCD Signal

Processor with Precision Timing™ Core

AD9972

Rev. SpA

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2006 Analog Devices, Inc. All rights reserved.

FEATURES OF EACH CHANNEL

1.8 V analog and digital core supply voltage

Correlated double sampler (CDS) with

−3 dB, 0 dB, +3 dB, and +6 dB gain

6 dB to 42 dB, 10-bit variable gain amplifier (VGA)

14-bit, 40 MHz analog-to-digital converter (ADC)

Black level clamp with variable level control

Complete on-chip timing generator

Precision Timing core with 400 ps resolution @ 40 MHz

On-chip 3 V horizontal and RG drivers

100-lead, 9 mm × 9 mm, 0.8 mm pitch, CSP_BGA package

Internal LDO regulator circuitry

APPLICATIONS

Professional HDTV camcorders

Professional/high end digital cameras

Broadcast cameras

Industrial high speed cameras

GENERAL DESCRIPTION

The AD9972 is a highly integrated, dual-channel CCD signal

processor for high speed digital video camera applications. Each

channel is specified at pixel rates of up to 40 MHz. The AD9972

consists of a complete analog front end with analog-to-digital

conversion combined with a programmable timing driver. The

Precision Timing core allows adjustment of high speed clocks

with approximately 400 ps resolution at 40 MHz operation.

Each analog front end includes black level clamping, CDS, VGA,

and a 40 MSPS, 14-bit ADC. The timing driver provides the high

speed CCD clock drivers for the RG_A, RG_B, H1_A to H4_A,

and H1_B to H4_B outputs. A 3-wire serial interface is used to

program each channel of the AD9972.

Available in a space-saving, 9 mm × 9 mm, CSP_BGA package,

the AD9972 is specified over an operating temperature range of

−25°C to +85°C.

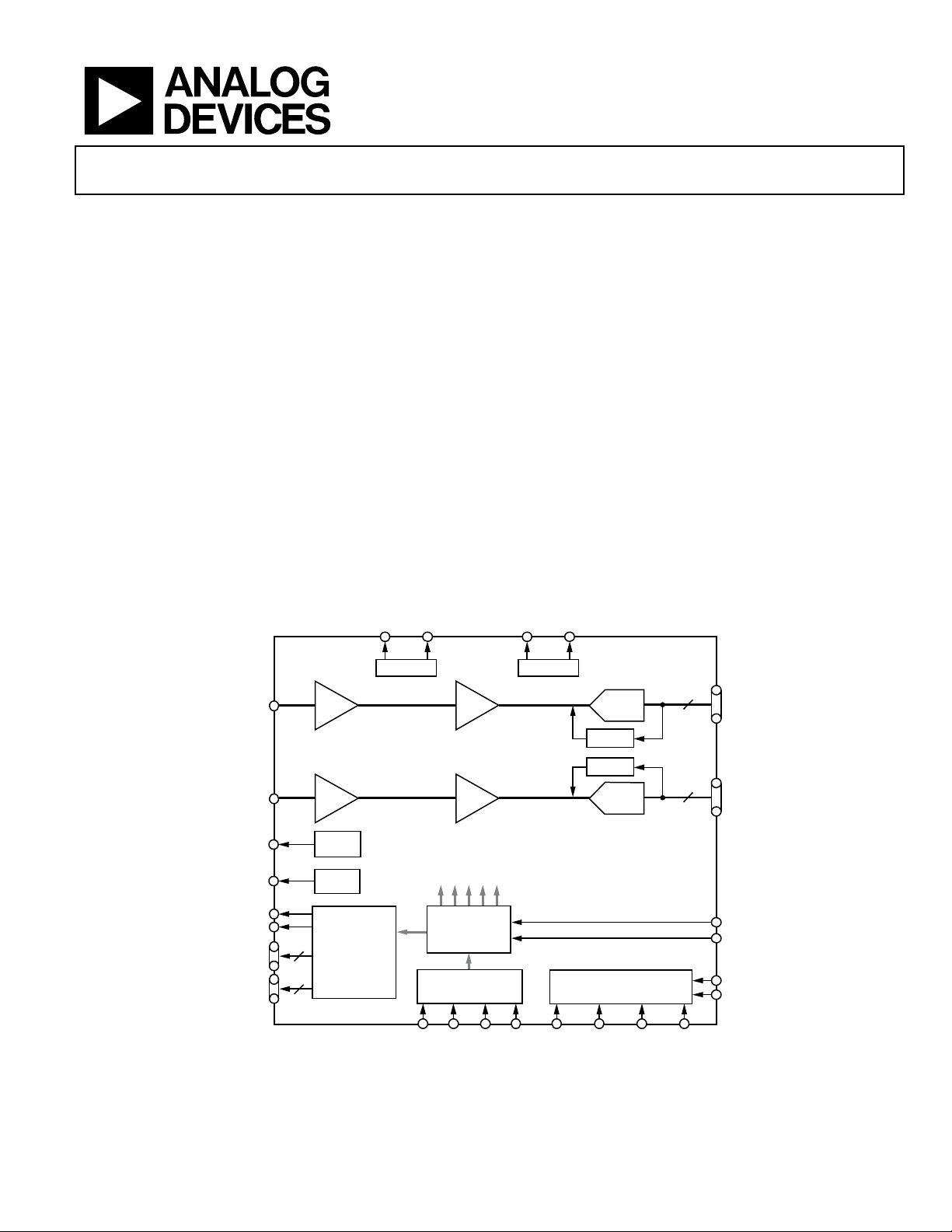

FUNCTIONAL BLOCK DIAGRAM

AD9972

SYNC

GENERATOR

PRECISION

TIMING

CORE

INTERNAL CLOCKS

HORIZONTAL

DRIVERS

RG_B

RG_A

H1_A TO H4_A

4

H1_B TO H4_B

4

HD_A VD_A HD_B VD_B

INTERNAL

REGISTERS

SL_A

SDATA_A

SL_B

SDATA_B

SCK_A

SCK_B

CLI_A

CLI_B

CLAMP

DOUT_A

CCDIN_A

6dB

~

42dB

VGA

ADC

CDS

14

CLAMP

DOUT_B

CCDIN_B

6dB

~

42dB

VGA

ADC

CDS

14

REFT_B REFB_B

VREF_B

REFT_

A

REFB_

A

VREF_A

–3, 0, +3, +6dB

–3, 0, +3, +6dB

1.8V OUTPUT LDO A

1.8V OUTPUT LDO B

0

5866-001

Figure 1.

For more information on the AD9772, contact Analog Devices, Inc. at: afe.ccd@analog.com.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件