Datasheet 搜索 > 比较器 > ADI(亚德诺) > ADCMP604BKSZ-REEL7 数据手册 > ADCMP604BKSZ-REEL7 数据手册 5/14 页

器件3D模型

器件3D模型¥ 31.106

ADCMP604BKSZ-REEL7 数据手册 - ADI(亚德诺)

制造商:

ADI(亚德诺)

分类:

比较器

封装:

SC-70-6

描述:

ANALOG DEVICES ADCMP604BKSZ-REEL7 模拟比较器, 单路, 高速, 1, 1.6 ns, 2.5V 至 5.5V, SC-70, 6 引脚

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

ADCMP604BKSZ-REEL7数据手册

Page:

of 14 Go

若手册格式错乱,请下载阅览PDF原文件

Data Sheet ADCMP604/ADCMP605

TIMING INFORMATION

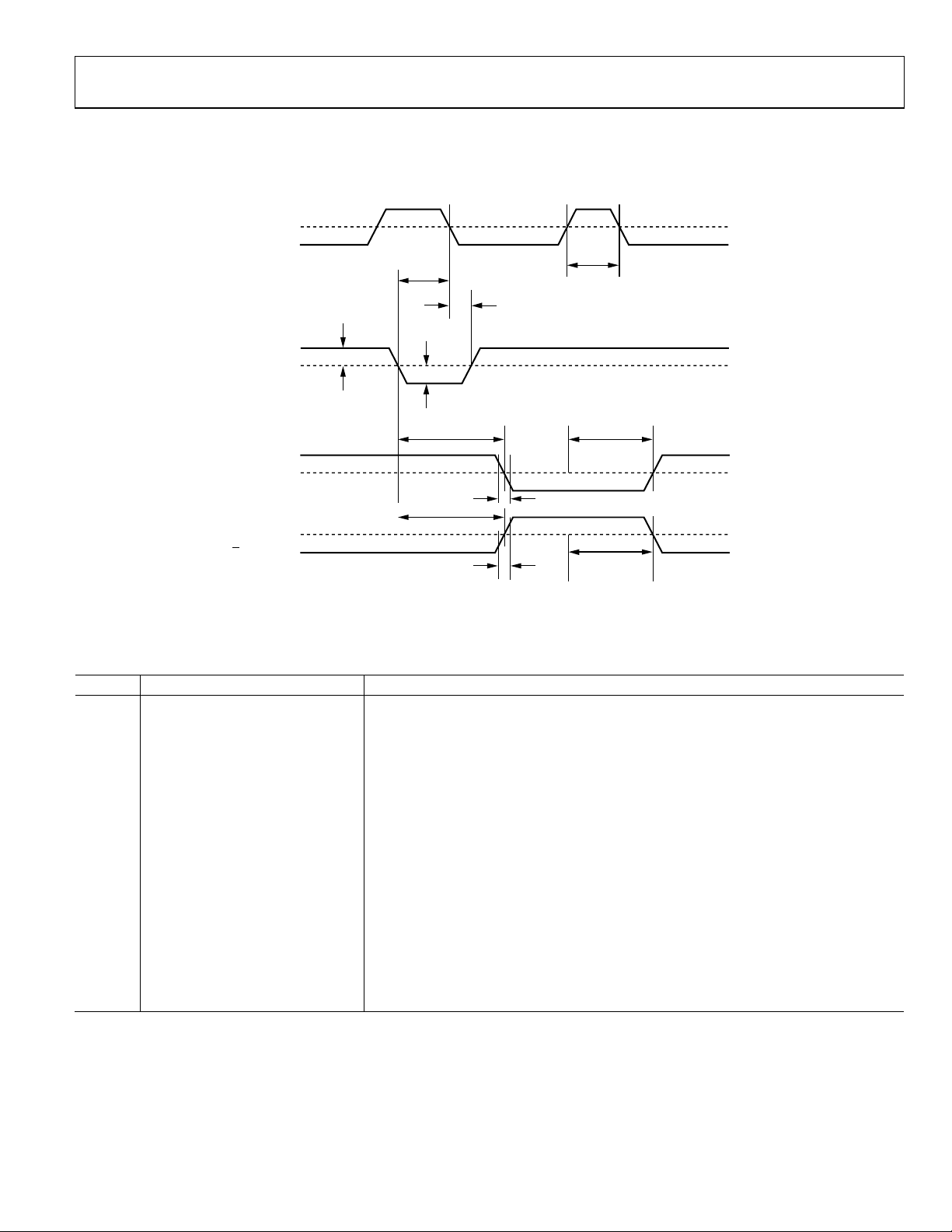

Figure 2 illustrates the ADCMP604/ADCMP605 latch timing relationships. Table 2 provides definitions of the terms shown in Figure 2.

1.1V

50%

V

N

± V

OS

DIFFERENTIAL

INPUT VOLTAGE

LATCH ENABLE

Q OUTPUT

t

H

t

PDL

t

PLOH

t

F

V

IN

V

OD

t

S

t

PL

50%

Q OUTPUT

t

PDH

t

PLOL

t

R

05916-025

Figure 2. System Timing Diagram

Table 2. Timing Descriptions

Symbol Timing Description

t

PDH

Input-to-Output High Delay Propagation delay measured from the time the input signal crosses the reference

(± the input offset voltage) to the 50% point of an output low-to-high transition.

t

PDL

Input-to-Output Low Delay Propagation delay measured from the time the input signal crosses the reference

(± the input offset voltage) to the 50% point of an output high-to-low transition.

t

PLOH

Latch Enable-to-Output High Delay

Propagation delay measured from the 50% point of the latch enable signal low-to-high

transition to the 50% point of an output low-to-high transition.

t

PLOL

Latch Enable-to-Output Low Delay Propagation delay measured from the 50% point of the latch enable signal low-to-high

transition to the 50% point of an output high-to-low transition.

t

H

Minimum Hold Time Minimum time after the negative transition of the latch enable signal that the input signal

must remain unchanged to be acquired and held at the outputs.

t

PL

Minimum Latch Enable Pulse Width Minimum time that the latch enable signal must be high to acquire an input signal change.

t

S

Minimum Setup Time Minimum time before the negative transition of the latch enable signal occurs that an

input signal change must be present to be acquired and held at the outputs.

t

R

Output Rise Time Amount of time required to transition from a low to a high output as measured at the

20% and 80% points.

t

F

Output Fall Time Amount of time required to transition from a high to a low output as measured at the

20% and 80% points.

V

OD

Voltage Overdrive Difference between the input voltages, V

A

and V

B

.

Rev. C | Page 5 of 14

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件