Datasheet 搜索 > 微控制器 > ADI(亚德诺) > ADUC7020BCPZ62-RL 数据手册 > ADUC7020BCPZ62-RL 数据手册 18/92 页

¥ 70.491

ADUC7020BCPZ62-RL 数据手册 - ADI(亚德诺)

制造商:

ADI(亚德诺)

分类:

微控制器

封装:

LFCSP EP

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P17P18P20P21P23P26P61Hot

原理图在P1P5P77P78P79

封装尺寸在P88

焊盘布局在P85

型号编码规则在P1P5P40P87P90

焊接温度在P16

功能描述在P4P17P18P21P23P26P61

技术参数、封装参数在P1P6P9P16P31P43

应用领域在P1

电气规格在P28

导航目录

ADUC7020BCPZ62-RL数据手册

Page:

of 92 Go

若手册格式错乱,请下载阅览PDF原文件

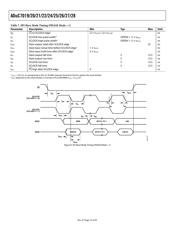

ADuC7019/20/21/22/24/25/26/27/28

Rev. B | Page 18 of 92

04955-066

ADuC7022

TOP VIEW

(Not to Scale)

PIN 1

INDICATOR

1

2

3

4

5

6

7

8

9

10

ADC5

ADC6

ADC7

ADC8

ADC9

GND

REF

TMS

TDI

BM/P0.0/CMP

OUT

/PLAI[7]

P0.6/T1/MRST/PLAO[3]

P1.2/SPM2/PLAI[2]

P1.3/SPM3/PLAI[3]

P1.4/SPM4/PLAI[4]/IRQ2

P1.5/SPM5/PLAI[5]/IRQ3

P1.6/SPM6/PLAI[6]

P1.7/SPM7/PLAO[0]

XCLKI

XCLKO

P0.7/ECLK/XCLK/SPM8/PLAO[4]

P2.0/SPM9/PLAO[5]/CONV

START

30

29

28

27

26

25

24

23

22

21

11

12

13

14

15

16

17

18

19

20

TCK

TDO

IOGND

IOV

DD

LV

DD

DGND

P0.3/TRST/ADC

BUSY

RST

IRQ0/P0.4/PWM

TRIP

/PLAO[1]

IRQ1/P0.5/ADC

BUSY

/PLAO[2]

ADC4

ADC3/CMP1

ADC2/CMP0

ADC1

ADC0

AV

DD

AGND

V

REF

P1.0/T1/SPM0/PLAI[0]

P1.1/SPM1/PLAI[1]

40

39

38

37

36

35

34

33

32

31

Figure 12. 40-Lead LFCSP_VQ Pin Configuration (ADuC7022)

Table 10. Pin Function Descriptions (ADuC7019/ADuC7020/ADuC7021/ADuC7022)

Pin No.

7019/7020 7021 7022 Mnemonic Description

38 37 36 ADC0 Single-Ended or Differential Analog Input 0.

39 38 37 ADC1 Single-Ended or Differential Analog Input 1.

40 39 38 ADC2/CMP0 Single-Ended or Differential Analog Input 2/Comparator Positive Input.

1 40 39 ADC3/CMP1

Single-Ended or Differential Analog Input 3 (Buffered Input on ADuC7019)/

Comparator Negative Input.

2 1 40 ADC4 Single-Ended or Differential Analog Input 4.

‒

2 1 ADC5 Single-Ended or Differential Analog Input 5.

‒

3 2 ADC6 Single-Ended or Differential Analog Input 6.

‒

4 3 ADC7 Single-Ended or Differential Analog Input 7.

‒ ‒

4 ADC8 Single-Ended or Differential Analog Input 8.

‒ ‒

5 ADC9 Single-Ended or Differential Analog Input 9.

3 5 6 GND

REF

Ground Voltage Reference for the ADC. For optimal performance, the

analog power supply should be separated from IOGND and DGND.

4 6

‒

DAC0/ADC12 DAC0 Voltage Output/Single-Ended or Differential Analog Input 12.

5 7

‒

DAC1/ADC13 DAC1 Voltage Output/Single-Ended or Differential Analog Input 13.

6

‒ ‒

DAC2/ADC14 DAC2 Voltage Output/Single-Ended or Differential Analog Input 14.

7

‒ ‒

DAC3/ADC15

DAC3 Voltage Output on ADuC7020. On the ADuC7019, a 10 nF capacitor

needs to be connected between this pin and AGND/Single-Ended or

Differential Analog Input 15.

8 8 7 TMS Test Mode Select, JTAG Test Port Input. Debug and download access.

9 9 8 TDI Test Data In, JTAG Test Port Input. Debug and download access.

10 10 9 BM/P0.0/CMP

OUT

/PLAI[7]

Multifunction I/O Pin. Boot Mode (BM). The ADuC7019/20/21/22 enter

serial download mode if BM is low at reset and execute code if BM is

pulled high at reset through a 1 kΩ resistor/General-Purpose Input and

Output Port 0.0/Voltage Comparator Output/Programmable Logic Array

Input Element 7.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件