Datasheet 搜索 > 接口隔离器 > ADI(亚德诺) > ADUM4160BRIZ 数据手册 > ADUM4160BRIZ 数据手册 3/17 页

器件3D模型

器件3D模型¥ 9.405

ADUM4160BRIZ 数据手册 - ADI(亚德诺)

制造商:

ADI(亚德诺)

分类:

接口隔离器

封装:

SOIC-16

描述:

ANALOG DEVICES ADUM4160BRIZ. 芯片, 数字隔离器, 70NS, SOIC-16

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P8Hot

典型应用电路图在P10

原理图在P1

封装尺寸在P14

型号编码规则在P14

封装信息在P4

功能描述在P1P8P10

技术参数、封装参数在P1P3P5P7

应用领域在P1P10P11

电气规格在P3

导航目录

ADUM4160BRIZ数据手册

Page:

of 17 Go

若手册格式错乱,请下载阅览PDF原文件

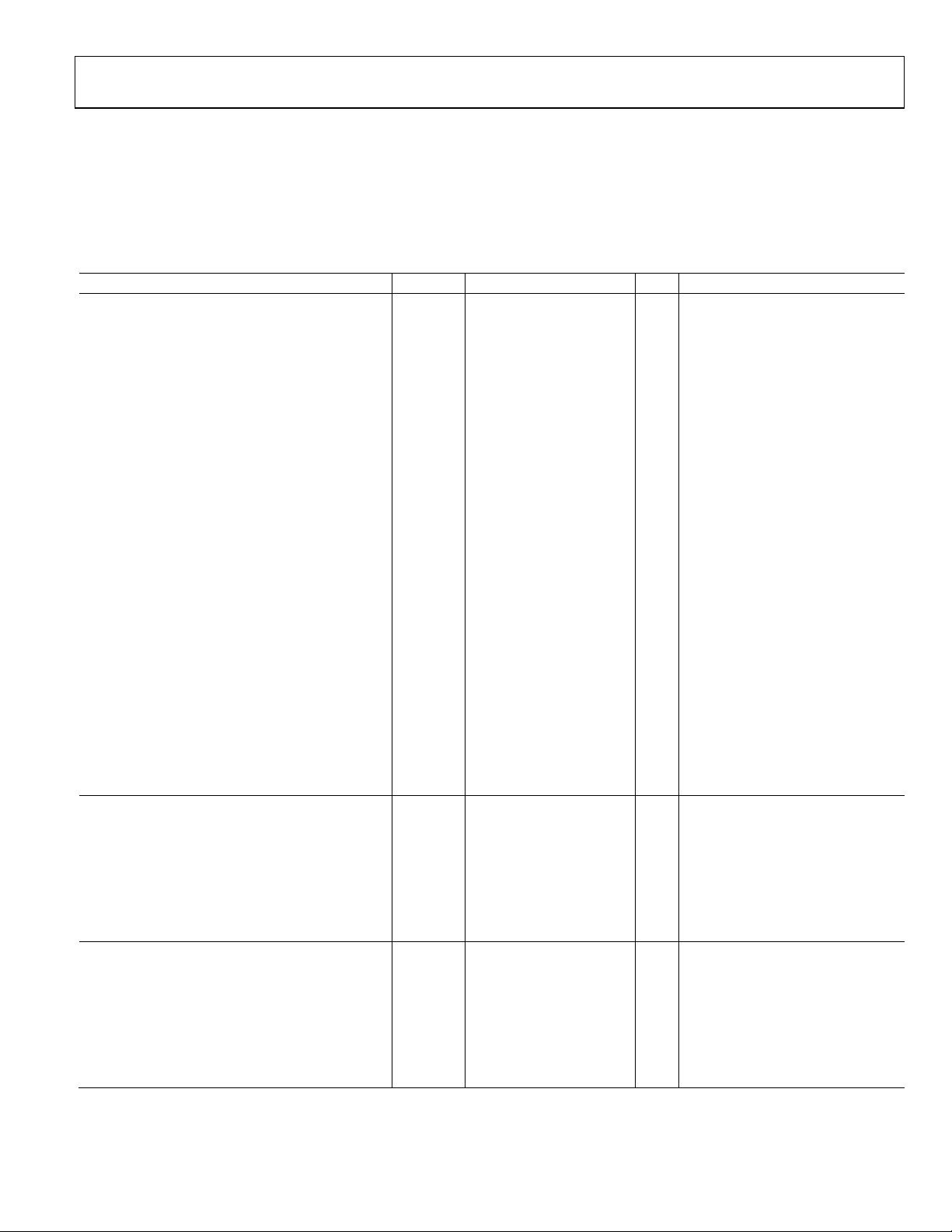

Data Sheet ADuM4160

Rev. D | Page 3 of 16

SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

4.5 V ≤ V

BUS1

≤ 5.5 V, 4.5 V ≤ V

BUS2

≤ 5.5 V; 3.1 V ≤ V

DD1

≤ 3.6 V, 3.1 V ≤ V

DD2

≤ 3.6 V; all minimum/maximum specifications apply over

the entire recommended operation range, unless otherwise noted; all typical specifications are at T

A

= 25°C, V

DD1

= V

DD2

= 3.3 V. Each

voltage is relative to its respective ground.

Table 1.

Parameter Symbol Min Typ Max Unit Test Conditions

DC SPECIFICATIONS

Total Supply Current

1

1.5 Mbps

V

DD1

or V

BUS1

Supply Current I

DD1 (L)

5 7 mA 750 kHz logic signal rate C

L

= 450 pF

V

DD2

or V

BUS2

Supply Current I

DD2 (L)

5 7 mA 750 kHz logic signal rate C

L

= 450 pF

12 Mbps

V

DD1

or V

BUS1

Supply Current I

DD1 (F)

6 8 mA 6 MHz logic signal rate C

L

= 50 pF

V

DD2

or V

BUS2

Supply Current I

DD2 (F)

6 8 mA 6 MHz logic signal rate C

L

= 50 pF

Idle Current

V

DD1

or V

BUS1

Idle Current I

DD1 (I)

1.7 2.3 mA

Input Currents

I

DD−

, I

DD+

,

I

UD+

, I

UD−

,

I

SPD

, I

PIN

,

I

SPU

, I

PDEN

−1 +0.1 +1 μA

0 V ≤ V

DD−

, V

DD+

, V

UD+

, V

UD−

, V

SPD

, V

PIN

,

V

SPU

, V

PDEN

≤ 3.0

Single-Ended Logic High Input Threshold

V

IH

2.0 V

Single-Ended Logic Low Input Threshold

V

IL

0.8 V

Single-Ended Input Hysteresis V

HST

0.4 V

Differential Input Sensitivity V

DI

0.2 V |V

XD+

− V

XD−

|

Logic High Output Voltages V

OH

2.8 3.6 V R

L

= 15 kΩ, V

L

= 0 V

Logic Low Output Voltages V

OL

0 0.3 V R

L

= 1.5 kΩ, V

L

= 3.6 V

V

DD1

and V

DD2

Supply Undervoltage Lockout V

UVLO

2.4 3.1 V

V

BUS1

Supply Undervoltage Lockout V

UVLOB1

3.5 4.35 V

V

BUS2

Supply Undervoltage Lockout V

UVLOB2

3.5 4.4 V

Transceiver Capacitance C

IN

10 pF UD+, UD−, DD+, DD− to ground

Capacitance Matching 10 %

Full Speed Driver Impedance Z

OUTH

4 20 Ω

Impedance Matching 10 %

SWITCHING SPECIFICATIONS, I/O PINS LOW SPEED

Low Speed Data Rate 1.5 Mbps C

L

= 50 pF

Propagation Delay

2

t

PHLL

, t

PLHL

325 ns

C

L

= 50 pF, SPD = SPU = low,

V

DD1

, V

DD2

= 3.3 V

Side 1 Output Rise/Fall Time (10% to 90%) Low

Speed

t

RL

/t

FL

75 300 ns

C

L

= 450 pF, SPD = SPU = low,

V

DD1

, V

DD2

= 3.3 V

Low Speed Differential Jitter, Next Transition

|t

LJN

| 45 ns C

L

= 50 pF

Low Speed Differential Jitter, Paired Transition |t

LJP

| 15 ns C

L

= 50 pF

SWITCHING SPECIFICATIONS, I/O PINS FULL SPEED

Full Speed Data Rate 12 Mbps C

L

= 50 pF

Propagation Delay

2

t

PHLF

, t

PLHF

20 60 70 ns

C

L

= 50 pF, SPD = SPU = high,

V

DD1

, V

DD2

= 3.3 V

Output Rise/Fall Time (10% to 90%) Full Speed t

RF

/t

FF

4 20 ns

C

L

= 50 pF, SPD = SPU = high,

V

DD1

, V

DD2

= 3.3 V

Full Speed Differential Jitter, Next Transition

|t

FJ N

| 3 ns C

L

= 50 pF

Full Speed Differential Jitter, Paired Transition |t

FJ P

| 1 ns C

L

= 50 pF

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件