Datasheet 搜索 > 8位微控制器 > Microchip(微芯) > ATTINY24A-SSN 数据手册 > ATTINY24A-SSN 数据手册 128/299 页

器件3D模型

器件3D模型¥ 9.931

ATTINY24A-SSN 数据手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

8位微控制器

封装:

SOIC-14

描述:

8位 MCU微控制单元, AVR ATtiny Family ATtiny24 Series Microcontrollers, 20 MHz, 2 KB, 128 Byte, 14 引脚

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P8P9P61P294Hot

典型应用电路图在P128

原理图在P10P13P59P74P76P77P78P91P93P95P97P99

型号编码规则在P276P277P278P294

封装信息在P279P280P281P283P284P285P286P287P288

功能描述在P123

应用领域在P38

电气规格在P156

导航目录

ATTINY24A-SSN数据手册

Page:

of 299 Go

若手册格式错乱,请下载阅览PDF原文件

ATtiny24A/44A/84A

2020 Microchip Technology Inc. Data Sheet Complete DS40002269A-page 128

4. After eight bits containing slave address and data direction (read or write) have been

transferred, the slave counter overflows and the SCL line is forced low (D). If the slave

is not the one the master has addressed, it releases the SCL line and waits for a new

start condition.

5. When the slave is addressed, it holds the SDA line low during the acknowledgment

cycle before holding the SCL line low again (i.e., the USI Counter Register must be set

to 14 before releasing SCL at (D)). Depending on the R/W bit the master or slave

enables its output. If the bit is set, a master read operation is in progress (i.e., the slave

drives the SDA line) The slave can hold the SCL line low after the acknowledge (E).

6. Multiple bytes can now be transmitted, all in same direction, until a stop condition is

given by the master (F), or a new start condition is given.

If the slave is not able to receive more data it does not acknowledge the data byte it has last

received. When the master does a read operation it must terminate the operation by forcing the

acknowledge bit low after the last byte transmitted.

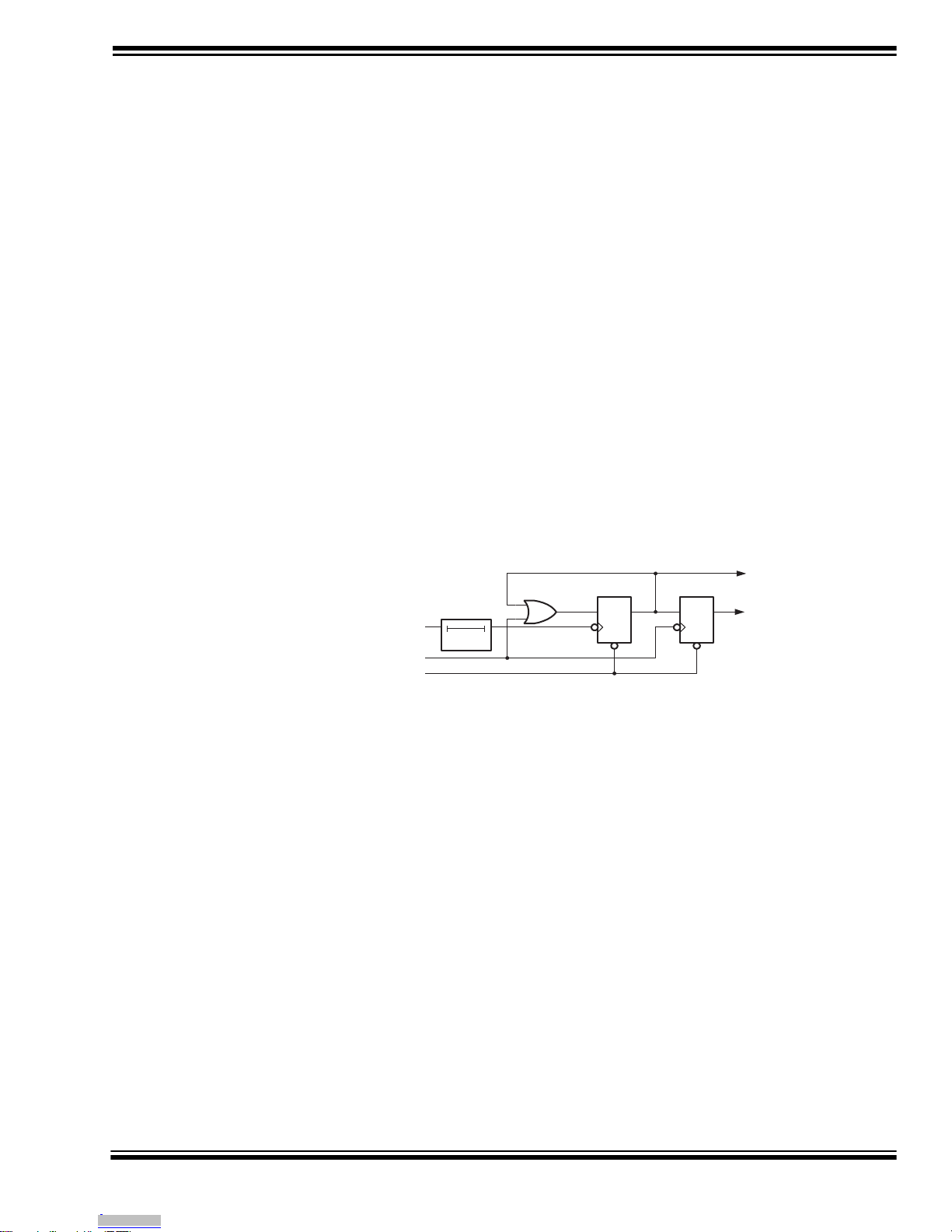

14.3.5 Start Condition Detector

The start condition detector is shown in Figure 14-6. The SDA line is delayed (in the range of 40

to 100 ns) to ensure valid sampling of the SCL line. The start condition detector is only enabled

in two-wire mode.

Figure 14-6. Start Condition Detector, Logic Diagram

The start condition detector works asynchronously and can therefore wake up the processor

from power-down sleep mode. However, the protocol used might have restrictions on the SCL

hold time. Therefore, when using this feature the oscillator start-up time (set by CKSEL fuses,

see “Clock Sources” on page 31) must also be taken into consideration. Refer to the description

of the USISIF bit on page 134 for further details.

14.3.6 Clock speed considerations

Maximum frequency for SCL and SCK is f

CK

/ 2. This is also the maximum data transmit and

receive rate in both two- and three-wire mode. In two-wire slave mode the Two-wire Clock Con-

trol Unit will hold the SCL low until the slave is ready to receive more data. This may reduce the

actual data rate in two-wire mode.

SDA

SCL

Write( USISIF)

CLOCK

HOLD

USISIF

DQ

CLR

DQ

CLR

Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from