Datasheet 搜索 > 微控制器 > ATMEL(爱特美尔) > ATTINY85V-10SU 数据手册 > ATTINY85V-10SU 数据手册 7/236 页

器件3D模型

器件3D模型¥ 9.824

ATTINY85V-10SU 数据手册 - ATMEL(爱特美尔)

制造商:

ATMEL(爱特美尔)

分类:

微控制器

封装:

SOIC-8

描述:

ATMEL ATTINY85V-10SU 微控制器, 8位, 低功率高性能, ATtiny, 10 MHz, 8 KB, 512 Byte, 8 引脚, SOIC

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P2P57Hot

典型应用电路图在P117

原理图在P4P7P55P67P70P71P73P87P88P99P100P111

封装尺寸在P212P213P214P215P216P224

型号编码规则在P209P210P211P226P227

封装信息在P212

功能描述在P112

应用领域在P33

电气规格在P143P209P225

导航目录

ATTINY85V-10SU数据手册

Page:

of 236 Go

若手册格式错乱,请下载阅览PDF原文件

7

2586M–AVR–07/10

ATtiny25/45/85

4. AVR CPU Core

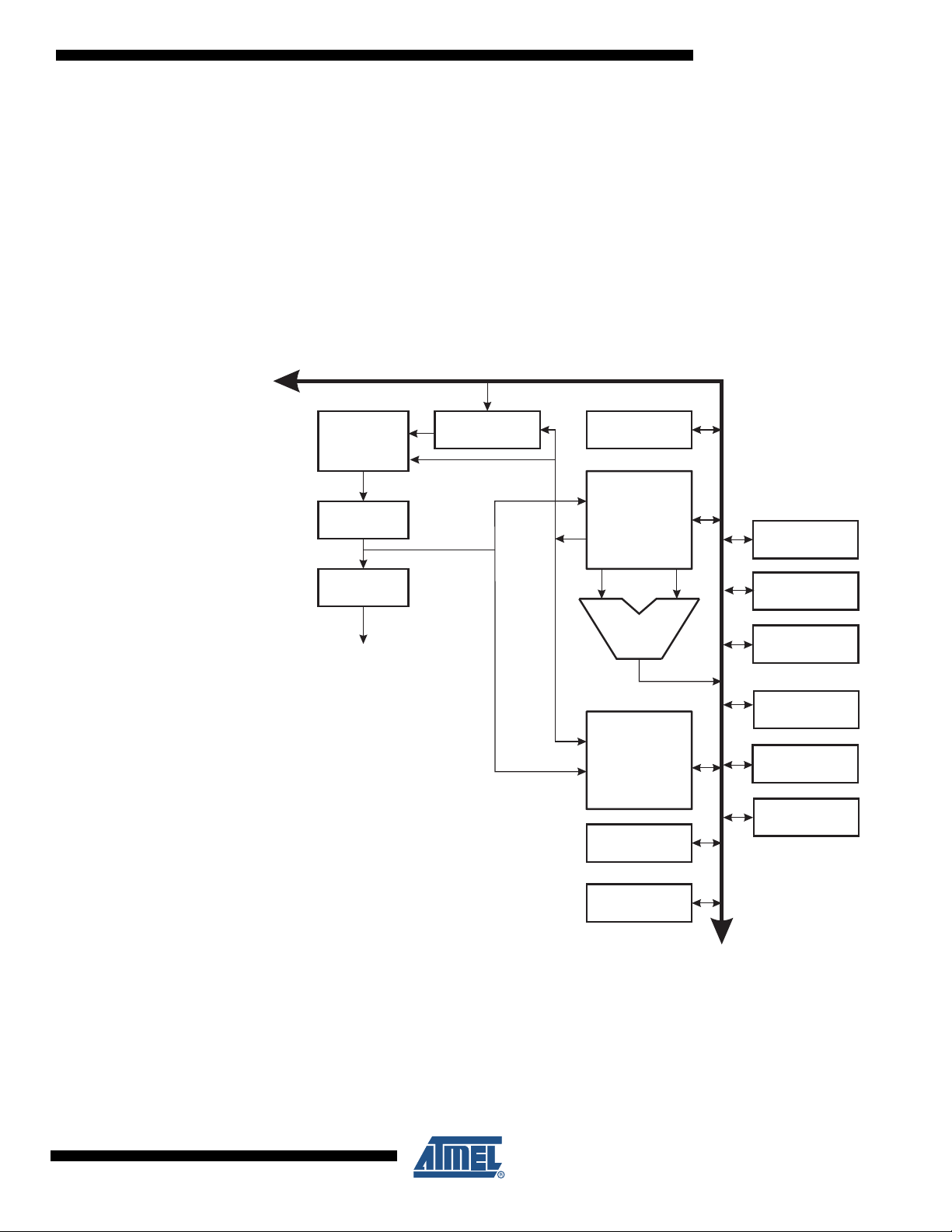

4.1 Introduction

This section discusses the AVR core architecture in general. The main function of the CPU core

is to ensure correct program execution. The CPU must therefore be able to access memories,

perform calculations, control peripherals, and handle interrupts.

4.2 Architectural Overview

Figure 4-1. Block Diagram of the AVR Architecture

In order to maximize performance and parallelism, the AVR uses a Harvard architecture – with

separate memories and buses for program and data. Instructions in the Program memory are

executed with a single level pipelining. While one instruction is being executed, the next instruc-

tion is pre-fetched from the Program memory. This concept enables instructions to be executed

in every clock cycle. The Program memory is In-System Reprogrammable Flash memory.

Flash

Program

Memory

Instruction

Register

Instruction

Decoder

Program

Counter

Control Lines

32 x 8

General

Purpose

Registrers

ALU

Status

and Control

I/O Lines

EEPROM

Data Bus 8-bit

Data

SRAM

Direct Addressing

Indirect Addressing

Interrupt

Unit

Watchdog

Timer

Analog

Comparator

I/O Module 2

I/O Module1

I/O Module n

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件