Datasheet 搜索 > 微控制器 > Silicon Labs(芯科) > C8051F124-GQ 数据手册 > C8051F124-GQ 数据手册 1/351 页

器件3D模型

器件3D模型¥ 240.2

C8051F124-GQ 数据手册 - Silicon Labs(芯科)

制造商:

Silicon Labs(芯科)

分类:

微控制器

封装:

TQFP-100

描述:

SILICON LABS C8051F124-GQ 微控制器, 8位, 混合信号, C8051F12x, 50 MHz, 128 KB, 8.25 KB, 100 引脚, TQFP

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P41P42P43P44P45P46P47P48P238P241P243Hot

典型应用电路图在P350

原理图在P21P22P23P24P25P26P31P33P34P36P37P55

封装尺寸在P51P54

型号编码规则在P20

封装信息在P1

技术参数、封装参数在P38P72P90P103P235

应用领域在P180

电气规格在P39P40P72P90P103P111P118P126P178P183P185P186

型号编号列表在P38

导航目录

C8051F124-GQ数据手册

Page:

of 351 Go

若手册格式错乱,请下载阅览PDF原文件

8K ISP FLASH MCU Family

C8051F120/1/2/3/4/5/6/7

Rev. 1.4 12/03 Copyright © 2003 by Silicon Laboratories C8051 F120/1/2/3/4/5/6/7 C8051 F130/1/2/3

Analog Peripherals

-

10 or 12-bit SAR ADC

• ± 1 LSB INL

• Programmable throughput up to 100 ksps

• Up to 8 external inputs; programmable as single-

ended or differential

• Programmable amplifier gain: 16, 8, 4, 2, 1, 0.5

• Data-dependent windowed interrupt generator

• Built-in temperature sensor

- 8-bit SAR ADC (‘F12x Only)

• Programmable throughput up to 500 ksps

• 8 external inputs (single-ended or differential)

• Programmable amplifier gain: 4, 2, 1, 0.5

- Two 12-bit DACs (‘F12x Only)

• Can synchronize outputs to timers for jitter-free wave-

form generation

- Two Analog Comparators

- Voltage Reference

- V

DD

Monitor/Brown-Out Detector

On-Chip JTAG Debug & Boundary Scan

-

On-chip debug circuitry facilitates full-speed, non-

intrusive in-circuit/in-system debugging

- Provides breakpoints, single-stepping, watchpoints,

stack monitor; inspect/modify memory and registers

- Superior performance to emulation systems using

ICE-chips, target pods, and sockets

- IEEE1149.1 compliant boundary scan

- Complete development kit

100-Pin TQFP or 64-Pin TQFP Packaging

-

Temperature Range: –40 to +85 °C

- RoHS Available

High Speed 8051 µC Core

-

Pipelined instruction architecture; executes 70% of

instruction set in 1 or 2 system clocks

- 100 MIPS or 50 MIPS throughput with on-chip PLL

- 2-cycle 16 x 16 MAC engine (C8051F120/1/2/3 and

C8051F130/1/2/3 only)

Memory

-

8448 bytes internal data RAM (8 k + 256)

- 128 or 64 kB Banked Flash; in-system programma-

ble in 1024-byte sectors

- External 64 kB data memory interface (programma-

ble multiplexed or non-multiplexed modes)

Digital Peripherals

-

8 byte-wide port I/O (100TQFP); 5 V tolerant

- 4 Byte-wide port I/O (64TQFP); 5 V tolerant

- Hardware SMBus™ (I2C™ Compatible), SPI™, and

two UART serial ports available concurrently

- Programmable 16-bit counter/timer array with

6 capture/compare modules

- 5 general purpose 16-bit counter/timers

- Dedicated watchdog timer; bi-directional reset pin

Clock Sources

-

Internal precision oscillator: 24.5 MHz

- Flexible PLL technology

- External Oscillator: Crystal, RC, C, or clock

Voltage Supples

-

Range: 2.7–3.6 V (50 MIPS) 3.0–3.6 V (100 MIPS)

- Power saving sleep and shutdown modes

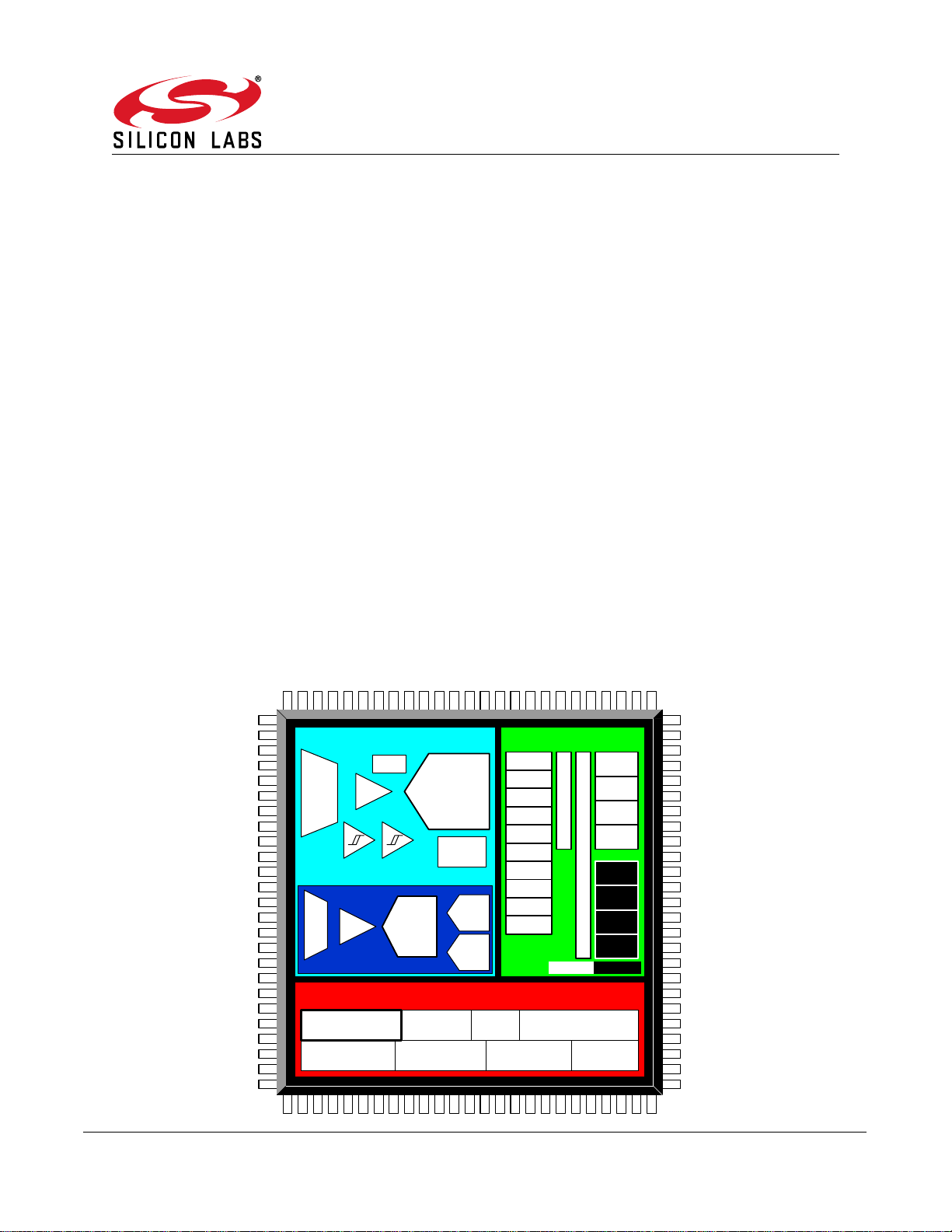

JTAG

128/64 kB

ISP FLASH

8448 B

SRAM

16 x 16 MAC

('F120/1/2/3, 'F13x)

+

-

10/12-bit

100ksps

ADC

CLOCK / PLL

CIRCUIT

PGA

VREF

12-Bit

DAC

TEMP

SENSOR

VOLTAGE

COMPARATORS

ANALOG PERIPHERALS

Port 0

Port 1

Port 2

Port 3

CROSSBAR

DIGITAL I/O

HIGH-SPEED CONTROLLER CORE

DEBUG

CIRCUITRY

20

INTERRUPTS

8051 CPU

(50 or 100MIPS)

12-Bit

DAC

+

-

8-bit

500ksps

ADC

Port 4

Port 5

Port 6

Port 7

External Memory Interface

100 pin64 pin

PGA

UART0

SMBus

SPI Bus

PCA

Timer 0

Timer 1

Timer 2

Timer 3

Timer 4

UART1

AMUX

AMUX

C8051F12x Only

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件