Datasheet 搜索 > 逻辑控制器 > TI(德州仪器) > CD74HCT4520ME4 数据手册 > CD74HCT4520ME4 数据手册 1/17 页

器件3D模型

器件3D模型¥ 0

CD74HCT4520ME4 数据手册 - TI(德州仪器)

制造商:

TI(德州仪器)

分类:

逻辑控制器

封装:

SOIC-16

描述:

高速CMOS逻辑双路同步计数器 High-Speed CMOS Logic Dual Synchronous Counters

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

CD74HCT4520ME4数据手册

Page:

of 17 Go

若手册格式错乱,请下载阅览PDF原文件

1

Data sheet acquired from Harris Semiconductor

SCHS216D

Features

• Positive or Negative Edge Triggering

• Synchronous Internal Carry Propagation

• Fanout (Over Temperature Range)

- Standard Outputs. . . . . . . . . . . . . . . 10 LSTTL Loads

- Bus Driver Outputs . . . . . . . . . . . . . 15 LSTTL Loads

• Wide Operating Temperature Range . . . -55

o

C to 125

o

C

• Balanced Propagation Delay and Transition Times

• Significant Power Reduction Compared to LSTTL

Logic ICs

• HC Types

- 2V to 6V Operation

- High Noise Immunity: N

IL

= 30%, N

IH

= 30% of V

CC

at V

CC

= 5V

• HCT Types

- 4.5V to 5.5V Operation

- Direct LSTTL Input Logic Compatibility,

V

IL

= 0.8V (Max), V

IH

= 2V (Min)

- CMOS Input Compatibility, I

l

≤ 1µA at V

OL

, V

OH

Description

The CD74HC4518 is a dual BCD up-counter. The ’HC4520

and CD74HCT4520 are dual binary up-counters. Each

device consists of two independent internally synchronous

4-stage counters. The counter stages are D-type flip-flops

having interchangeable CLOCK and ENABLE lines for

incrementing on either the positive-going or the negative-

going transition of CLOCK. The counters are cleared by high

levels on the MASTER RESET lines. The counter can be

cascaded in the ripple mode by connecting Q

3

to the

ENABLE input of the subsequent counter while the CLOCK

input of the latter is held low.

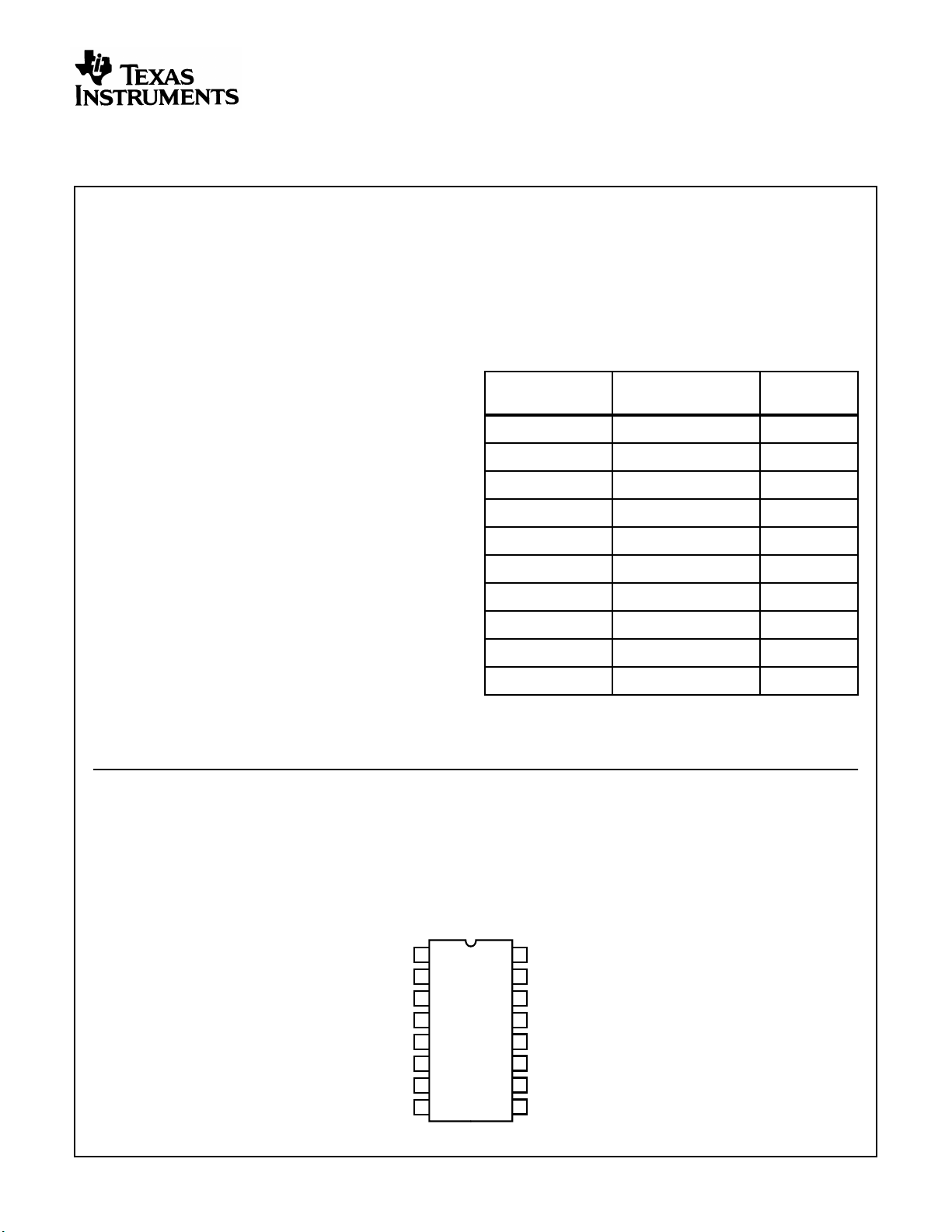

Pinout

CD54HC4520

(CERDIP)

CD74HC4518

(PDIP)

CD74HC4520, CD74HCT4520,

(PDIP, SOIC)

TOP VIEW

Ordering Information

PART NUMBER

TEMP. RANGE

(

o

C) PACKAGE

CD54HC4520F3A -55 to 125 16 Ld CERDIP

CD74HC4518E -55 to 125 16 Ld PDIP

CD74HC4520E -55 to 125 16 Ld PDIP

CD74HC4520M -55 to 125 16 Ld SOIC

CD74HC4520MT -55 to 125 16 Ld SOIC

CD74HC4520M96 -55 to 125 16 Ld SOIC

CD74HCT4520E -55 to 125 16 Ld PDIP

CD74HCT4520M -55 to 125 16 Ld SOIC

CD74HCT4520MT -55 to 125 16 Ld SOIC

CD74HCT4520M96 -55 to 125 16 Ld SOIC

NOTE: When ordering, use the entire part number. The suffix 96

denotes tape andreel.The suffix T denotesa small-quantity reel

of 250.

14

15

16

9

13

12

11

10

1

2

3

4

5

7

6

8

1CP

1E

1Q

0

1Q

1

1Q

2

1Q

3

GND

1MR

V

CC

2Q

3

2Q

2

2Q

1

2Q

0

2E

2CP

2MR

November 1997 - Revised October 2003

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright

© 2003, Texas Instruments Incorporated

CD74HC4518, CD54HC4520,

CD74HC4520, CD74HCT4520

High-Speed CMOS Logic

Dual Synchronous Counters

[

/Title

(

CD74

H

C451

8

,

C

D74

H

C452

0

,

C

D74

H

CT45

2

0)

/

Sub-

j

ect

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件