Datasheet 搜索 > National Semiconductor(美国国家半导体) > CGS74CT2524 数据手册 > CGS74CT2524 数据手册 1/6 页

¥ 0

CGS74CT2524 数据手册 - National Semiconductor(美国国家半导体)

制造商:

National Semiconductor(美国国家半导体)

描述:

1至4最小歪斜( 300 PS )时钟驱动器 1 to 4 Minimum Skew (300 ps) Clock Driver

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

CGS74CT2524数据手册

Page:

of 6 Go

若手册格式错乱,请下载阅览PDF原文件

TL/F/11752

CGS74CT2524 1 to 4 Minimum Skew (300 ps) Clock Driver

September 1995

CGS74CT2524

1 to 4 Minimum Skew (300 ps) Clock Driver

General Description

These minimum skew clock drivers are designed for Clock

Generation and Support (CGS) applications operating at

high frequencies. This device guarantees minimum output

skew across the outputs of a given device.

Skew parameters are also provided as a means to measure

duty cycle requirements as those found in high speed clock-

ing systems. The CGS74CT2524 is a minimum skew clock

driver with one input driving four outputs, specifically de-

signed for signal generation and clock distribution applica-

tions.

Features

Y

Guaranteed 300 ps pin-to-pin skew (t

OSHL

and t

OSLH

)

Y

Implemented on National’s FACT

TM

family process

Y

1 input to 4 outputs low skew clock distribution

Y

Symmetric output current drive: 24 mA I

OH

/I

OL

Y

Industrial temperature of

b

40

§

Cto

a

85

§

C

Y

8-pin SOIC package

Y

Low dynamic power consumption above 20 MHz

Y

Guaranteed 2 kV ESD protection

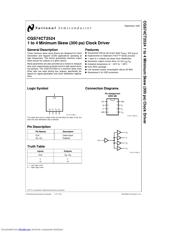

Logic Symbol

TL/F/11752–1

The output pins act as a single entity and will follow the state of the CLK

when the clock distribution chip is selected.

Pin Description

Pin Names Descripton

CLK Clock Input

O

0

–O

3

Outputs

Truth Table

Inputs Outputs

CLK O

0

–O

3

LL

HH

L

e

Low Logic Level

H

e

High Logic Level

Connection Diagrams

Pin Assignment

SOIC (M)

TL/F/11752–2

TL/F/11752–3

FACT

TM

is a trademark of National Semiconductor Corporation.

C

1995 National Semiconductor Corporation RRD-B30M115/Printed in U. S. A.

Downloaded from Elcodis.com electronic components distributor

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件