Datasheet 搜索 > 微控制器 > Cypress Semiconductor(赛普拉斯) > CY7C64215-56LTXCT 数据手册 > CY7C64215-56LTXCT 数据手册 1/45 页

器件3D模型

器件3D模型¥ 14.868

CY7C64215-56LTXCT 数据手册 - Cypress Semiconductor(赛普拉斯)

制造商:

Cypress Semiconductor(赛普拉斯)

分类:

微控制器

封装:

QFN-56

描述:

USB转换芯片 CY7C64215-56LTXCT QFN-56-EP(8x8)

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

原理图在P1P3P4

封装尺寸在P30P31

型号编码规则在P33

封装信息在P30P33

焊接温度在P32

功能描述在P26

技术参数、封装参数在P12P13P14P15P16P17P18P19P20P21P22P23

应用领域在P3

电气规格在P12P14P24

型号编号列表在P40

导航目录

CY7C64215-56LTXCT数据手册

Page:

of 45 Go

若手册格式错乱,请下载阅览PDF原文件

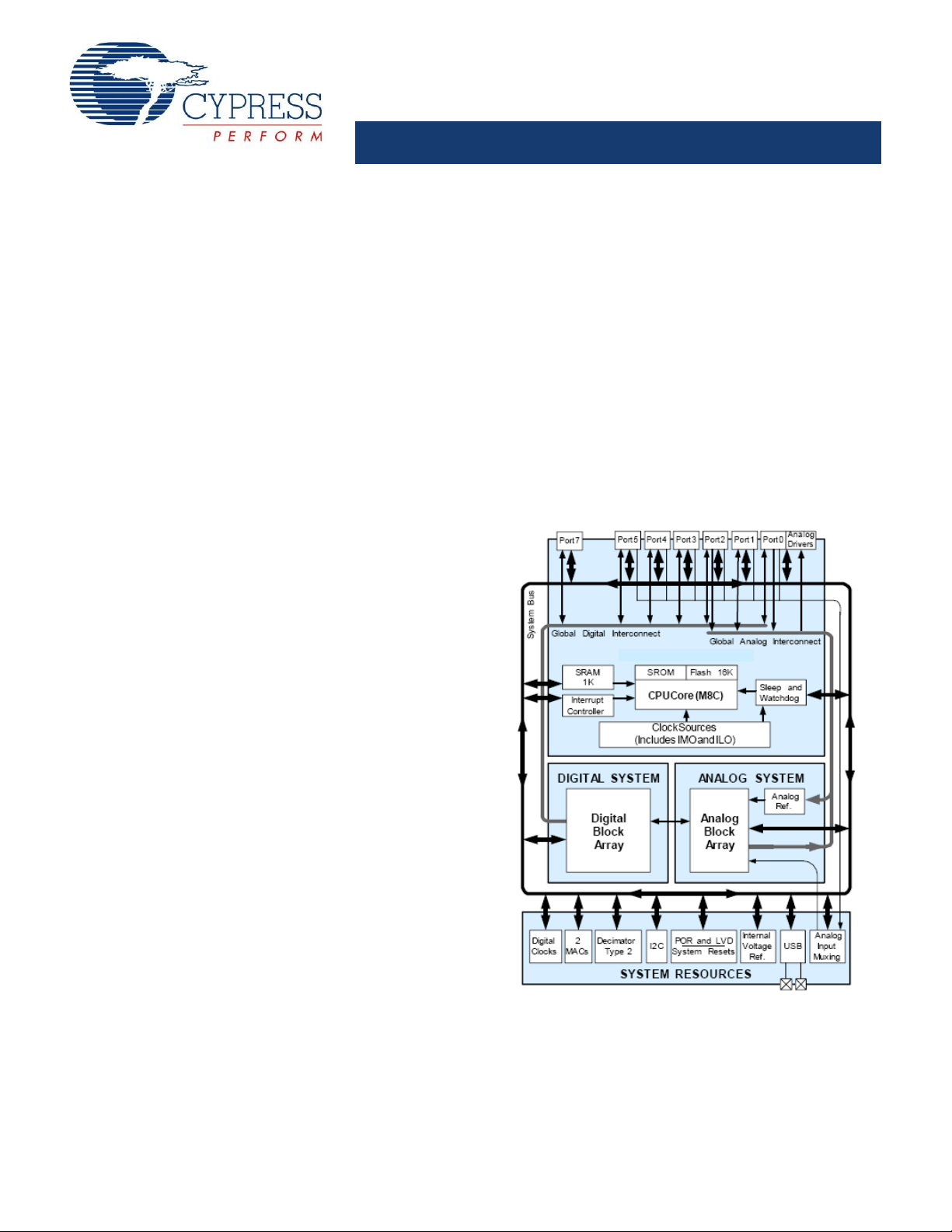

CY7C64215

enCoRe™ III Full-Speed USB Controller

Cypress Semiconductor Corporation • 198 Champion Court • San Jose, CA 95134-1709 • 408-943-2600

Document Number: 38-08036 Rev. *M Revised August 28, 2014

enCoRe™ III Full-Speed U SB Controller

Features

■ Powerful Harvard-architecture processor

❐ M8C processor speeds up to 24 MHz

❐ Two 8 × 8 multiply, 32-bit accumulate

❐ 3.15 to 5.25-V operating voltage

❐ USB 2.0 USB-IF certified. TID# 40000110

❐ Commercial operating temperature range: 0 °C to +70 °C

❐ Industrial operating temperature range: –40 °C to +85 °C

■ Advanced peripherals (enCoRe™ III blocks)

❐ Six analog enCoRe III blocks provide:

• Up to 14-bit incremental and delta sigma analog-to-digital

converters (ADCs)

❐ Programmable threshold comparator

❐ Four digital enCoRe III blocks provide:

• 8-bit and 16-bit pulse width modulators (PWMs), timers,

and counters

•I

2

C master

• SPI master or slave

• Full-duplex universal asynchronous receiver-transmitter

(UART)

• CYFISNP modules to talk to Cypress CYFI™ radio

■ Complex peripherals by combining blocks

■ Full-speed USB (12 Mbps)

❐ Four unidirectional endpoints

❐ One bidirectional control endpoint

❐ Dedicated 256-byte buffer

❐ No external crystal required

❐ Operational at 3.15 V to 3.5 V or 4.35 V to 5.25 V

■ Flexible on-chip memory

❐ 16 KB flash program storage 50,000 erase/write cycles

❐ 1 KB SRAM data storage

❐ In-system serial programming (ISSP)

❐ Partial flash updates

❐ Flexible protection modes

❐ EEPROM emulation in flash

■ Programmable pin configurations

❐ 25 mA sink on all general purpose I/Os (GPIOs)

❐ Pull-up, Pull-down, high Z, strong, or open drain drive modes

on all GPIOs

❐ Configurable interrupt on all GPIOs

■ Precision, programmable clocking

❐ Internal ±4% 24- and 48-MHz oscillator with support for

external clock oscillator

❐ Internal oscillator for watchdog and sleep

❐ .25% accuracy for USB with no external components

■ Additional system resources

❐ Inter-integrated circuit (I

2

C) slave, master, and multimaster

to 400 kHz

❐ Watchdog and sleep timers

❐ User-configurable low-voltage detection (LVD)

❐ Integrated supervisory circuit

❐ On-chip precision voltage reference

■ Complete development tools

❐ Free development software (PSoC

®

Designer)

❐ Full-featured, in-circuit emulator and programmer

❐ Full-speed emulation

❐ Complex breakpoint structure

❐ 128 KB trace memory

enCoRe III Core

Block Diagram

Errata: For information on silicon errata, see “Errata” on page 40. Details include trigger conditions, devices affected, and proposed workaround.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件