Datasheet 搜索 > 微控制器 > Cypress Semiconductor(赛普拉斯) > CYUSB3014-BZXIT 数据手册 > CYUSB3014-BZXIT 数据手册 10/53 页

器件3D模型

器件3D模型¥ 87.113

CYUSB3014-BZXIT 数据手册 - Cypress Semiconductor(赛普拉斯)

制造商:

Cypress Semiconductor(赛普拉斯)

分类:

微控制器

封装:

BGA-121

描述:

USB 接口集成电路 32-bit 512KB RAM FX3 SuprSped USB Con

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

CYUSB3014-BZXIT数据手册

Page:

of 53 Go

若手册格式错乱,请下载阅览PDF原文件

CYUSB301X/CYUSB201X

Document Number: 001-52136 Rev. *S Page 10 of 53

Clocking

FX3 allows either a crystal to be connected between the XTALIN

and XTALOUT pins or an external clock to be connected at the

CLKIN pin. The XTALIN, XTALOUT, CLKIN, and CLKIN_32 pins

can be left unconnected if they are not used.

Crystal frequency supported is 19.2 MHz, while the external

clock frequencies supported are 19.2, 26, 38.4, and 52 MHz.

FX3 has an on-chip oscillator circuit that uses an external

19.2-MHz (±100 ppm) crystal (when the crystal option is used).

An appropriate load capacitance is required with a crystal. Refer

to the specification of the crystal used to determine the appro-

priate load capacitance. The FSLC[2:0] pins must be configured

appropriately to select the crystal- or clock-frequency option. The

configuration options are shown in Table 3.

Clock inputs to FX3 must meet the phase noise and jitter require-

ments specified in Table 4 on page 10.

The input clock frequency is independent of the clock and data

rate of the FX3 core or any of the device interfaces. The internal

PLL applies the appropriate clock multiply option depending on

the input frequency.

32-kHz Watchdog Timer Clock Input

FX3 includes a watchdog timer. The watchdog timer can be used to interrupt the ARM926EJ-S core, automatically wake up the FX3

in Standby mode, and reset the ARM926EJ-S core. The watchdog timer runs a 32-kHz clock, which may be optionally supplied from

an external source on a dedicated FX3 pin.

The firmware can disable the watchdog timer. Requirements for the optional 32-kHz clock input are listed in Table 5.

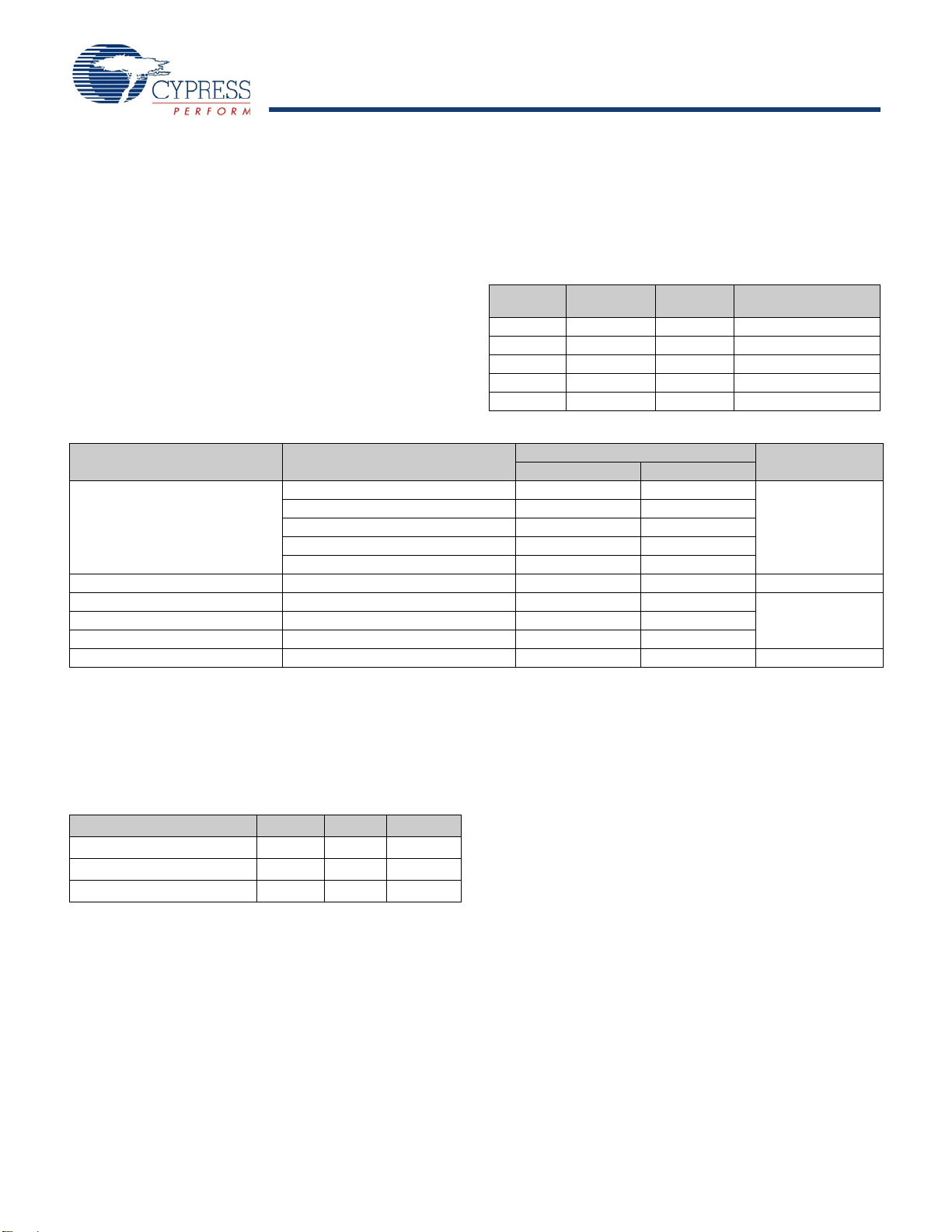

Table 3. Crystal/Clock Frequency Selection

FSLC[2] FSLC[1] FSLC[0]

Crystal/Clock

Frequency

0 0 0 19.2-MHz crystal

1 0 0 19.2-MHz input CLK

1 0 1 26-MHz input CLK

1 1 0 38.4-MHz input CLK

1 1 1 52-MHz input CLK

Table 4. FX3 Input Clock Specifications

Parameter Description

Specification

Units

Min Max

Phase noise

100-Hz offset – –75

dB

1-kHz offset – –104

10-kHz offset – –120

100-kHz offset – –128

1-MHz offset – –130

Maximum frequency deviation – – 150 ppm

Duty cycle – 30 70

%Overshoot – – 3

Undershoot – – –3

Rise time/fall time – – 3 ns

Table 5. 32-kHz Clock Input Requirements

Parameter Min Max Units

Duty cycle 40 60 %

Frequency deviation – ±200 ppm

Rise time/fall time – 200 ns

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件