Datasheet 搜索 > DA转换器 > TI(德州仪器) > DAC121S101EVAL 数据手册 > DAC121S101EVAL 数据手册 3/22 页

¥ 814.354

DAC121S101EVAL 数据手册 - TI(德州仪器)

制造商:

TI(德州仪器)

分类:

DA转换器

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

DAC121S101EVAL数据手册

Page:

of 22 Go

若手册格式错乱,请下载阅览PDF原文件

Ordering Information

Order Numbers Temperature Range Package Top Mark Feature

DAC121S101CIMM

−40°C ≤ T

A

≤ +105°C

MSOP

X60C

DAC121S101CIMMX

−40°C ≤ T

A

≤ +105°C

MSOP T/R

DAC121S101CIMK

−40°C ≤ T

A

≤ +105°C

TSOT

X61C

DAC121S101CIMKX

−40°C ≤ T

A

≤ +105°C

TSOT T/R

DAC121S101QCMK

−40°C ≤ T

A

≤ +125°C

TSOT

X61Q

AEC-Q100 Grade 1

Qualified; Automotive

Grade Production Flow

DAC121S101QCMKX

−40°C ≤ T

A

≤ +125°C

TSOT T/R

DAC121S101EVAL Evaluation Board TSOT

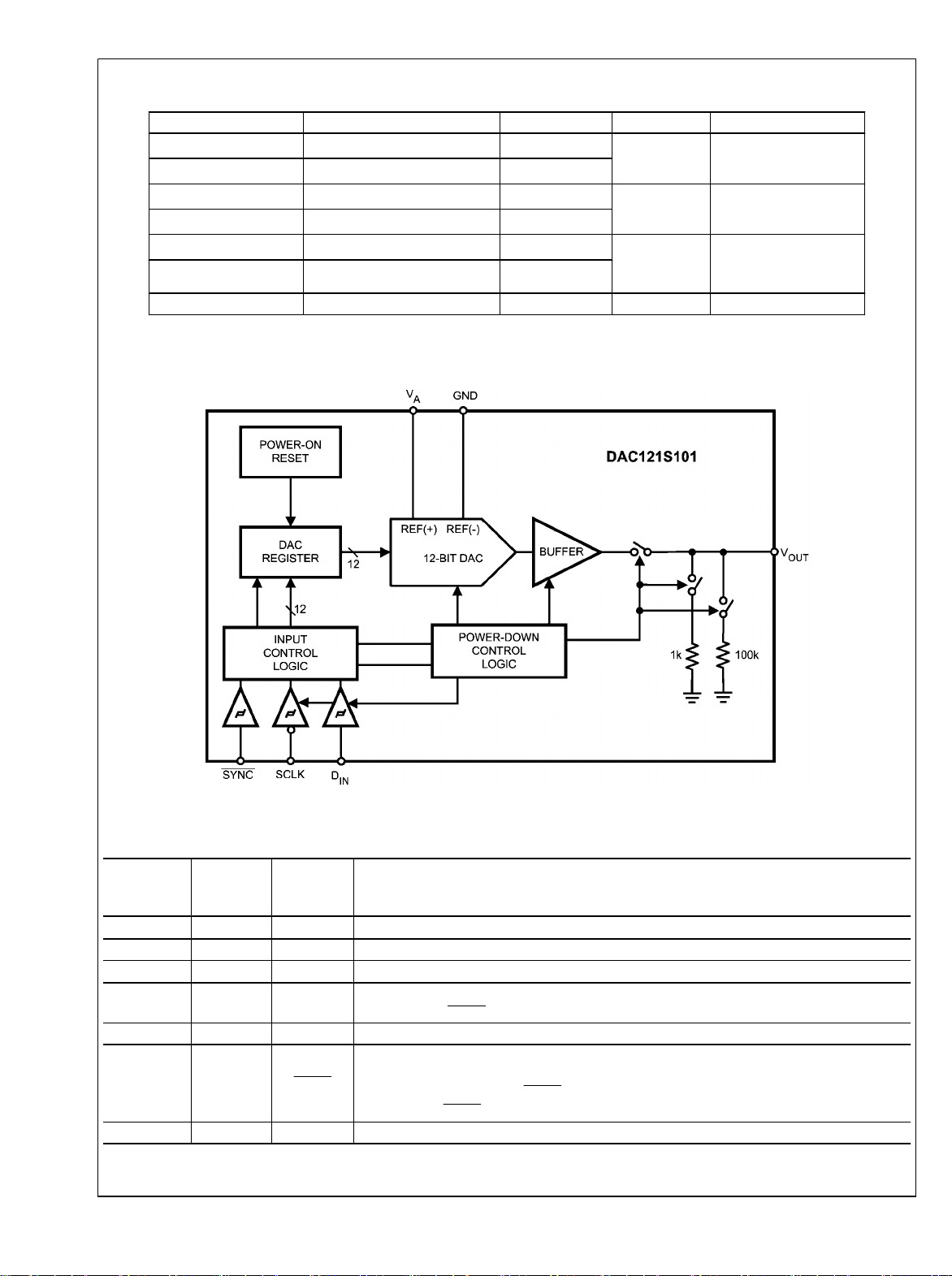

Block Diagram

20114903

Pin Descriptions

TSOT

(SOT-23)

Pin No.

MSOP

Pin No.

Symbol Description

1 4

V

OUT

DAC Analog Output Voltage.

2 8 GND Ground reference for all on-chip circuitry.

3 1

V

A

Power supply and Reference input. Should be decoupled to GND.

4 7

D

IN

Serial Data Input. Data is clocked into the 16-bit shift register on the falling edges of SCLK

after the fall of SYNC.

5 6 SCLK Serial Clock Input. Data is clocked into the input shift register on the falling edges of this pin.

6 5 SYNC

Frame synchronization input for the data input. When this pin goes low, it enables the input

shift register and data is transferred on the falling edges of SCLK. The DAC is updated on

the 16th clock cycle unless SYNC is brought high before the 16th clock, in which case the

rising edge of SYNC acts as an interrupt and the write sequence is ignored by the DAC.

2, 3 NC No Connect. There is no internal connection to these pins.

www.national.com 2

DAC121S101/DAC121S101Q

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件