Datasheet 搜索 > TI(德州仪器) > DS90UB947TRGCRQ1 数据手册 > DS90UB947TRGCRQ1 数据手册 14/81 页

器件3D模型

器件3D模型¥ 28.321

DS90UB947TRGCRQ1 数据手册 - TI(德州仪器)

制造商:

TI(德州仪器)

封装:

VQFN-64

描述:

1080p 双路 FPD-Link III 串行器 64-VQFN -40 to 105

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P3P4P5P70P71Hot

典型应用电路图在P65P66P67P68

原理图在P14

封装尺寸在P74P76P77

标记信息在P74

封装信息在P73P74P75P76P77

功能描述在P37P38P39P40P41P42P43P44P45P46P47P48

技术参数、封装参数在P6P73

应用领域在P1P65P66P67P68P81

电气规格在P7P8

导航目录

DS90UB947TRGCRQ1数据手册

Page:

of 81 Go

若手册格式错乱,请下载阅览PDF原文件

C1

C0

I2C

Interface

I2C

PAT

GEN

Open-LDI

Open-LDI

OLDI

Interface

Open LDI

Analog

Regs

Clocks

DFT

Audio

I2S

FPD3 TX

Analog

FPD-Link III

FPD3 TX

Analog

FPD-Link III

FPD-Link III TX

Digital

FPD-Link III TX

Digital

FPD3

Output

Select

Config

Single/Dual

Control

DS90UB947-Q1

SNLS454 –NOVEMBER 2014

www.ti.com

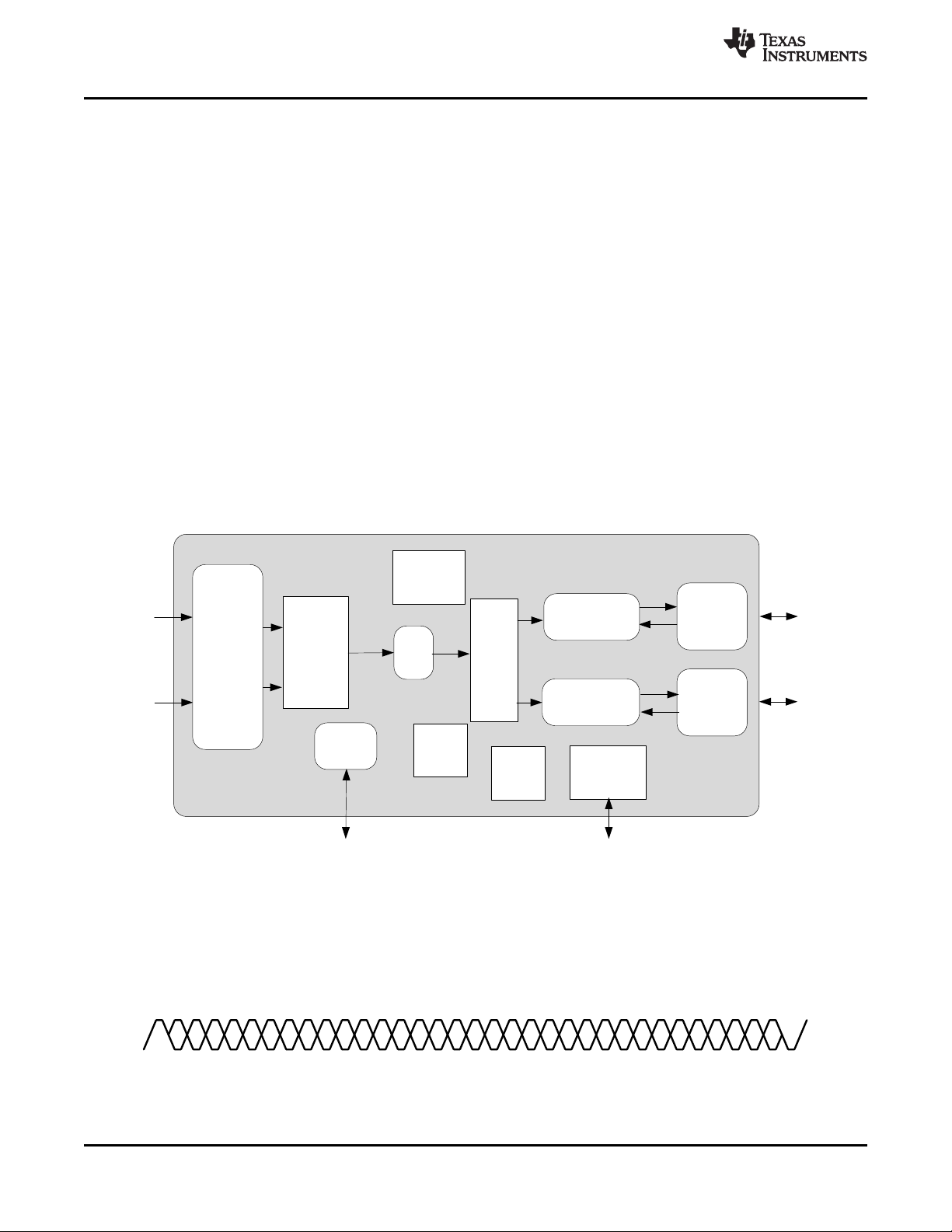

8 Detailed Description

8.1 Overview

The DS90UB947-Q1 converts a single or dual FPD-Link (Open LDI) interface (up to 8 LVDS lanes + 1 clock) to

an FPD-Link III interface. This device transmits a 35-bit symbol over a single serial pair operating up to 3.36Gbps

line rate, or two serial pairs operating up to 2.975Gbps line rate. The serial stream contains an embedded clock,

video control signals, RGB video data, and audio data. The payload is DC-balanced to enhance signal quality

and support AC coupling.

The DS90UB947-Q1 serializer is intended for use with a DS90UB926Q-Q1, DS90UB928Q-Q1, DS90UB940-Q1,

DS90UB948-Q1 deserializer.

The DS90UB947-Q1 serializer and companion deserializer incorporate an I2C compatible interface. The I2C

compatible interface allows programming of serializer or deserializer devices from a local host controller. In

addition, the devices incorporate a bidirectional control channel (BCC) that allows communication between

serializer/deserializer as well as remote I2C slave devices.

The bidirectional control channel (BCC) is implemented via embedded signaling in the high-speed forward

channel (serializer to deserializer) combined with lower speed signaling in the reverse channel (deserializer to

serializer). Through this interface, the BCC provides a mechanism to bridge I2C transactions across the serial

link from one I2C bus to another. The implementation allows for arbitration with other I2C compatible masters at

either side of the serial link.

8.2 Functional Block Diagram

8.3 Feature Description

8.3.1 High Speed Forward Channel Data Transfer

The High Speed Forward Channel is composed of 35 bits of data containing RGB data, sync signals, I2C,

GPIOs, and I2S audio transmitted from serializer to deserializer. Figure 12 illustrates the serial stream per clock

cycle. This data payload is optimized for signal transmission over an AC coupled link. Data is randomized,

balanced and scrambled.

Figure 12. FPD-Link III Serial Stream

14 Submit Documentation Feedback Copyright © 2014, Texas Instruments Incorporated

Product Folder Links: DS90UB947-Q1

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件