Datasheet 搜索 > 微处理器 > Silicon Labs(芯科) > EM357-RTR 数据手册 > EM357-RTR 数据手册 1/245 页

器件3D模型

器件3D模型¥ 21.772

EM357-RTR 数据手册 - Silicon Labs(芯科)

制造商:

Silicon Labs(芯科)

分类:

微处理器

封装:

QFN-48

描述:

射频收发器, O-QPSK, 2.4GHz至2.5GHz, 5Mbps, 8dBm输出, -102dBm输入, 2.1V至3.6V, QFN-48

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P5P6P216P222Hot

典型应用电路图在P223P224

原理图在P26P28P38P44P53P75P125P179P205P206P216P222

封装尺寸在P226

型号编码规则在P230

标记信息在P229

封装信息在P230P231

焊接温度在P228

功能描述在P2P26P28P126

技术参数、封装参数在P14P19P21P54P189P220

应用领域在P45

电气规格在P14P15P21P54

型号编号列表在P14

导航目录

EM357-RTR数据手册

Page:

of 245 Go

若手册格式错乱,请下载阅览PDF原文件

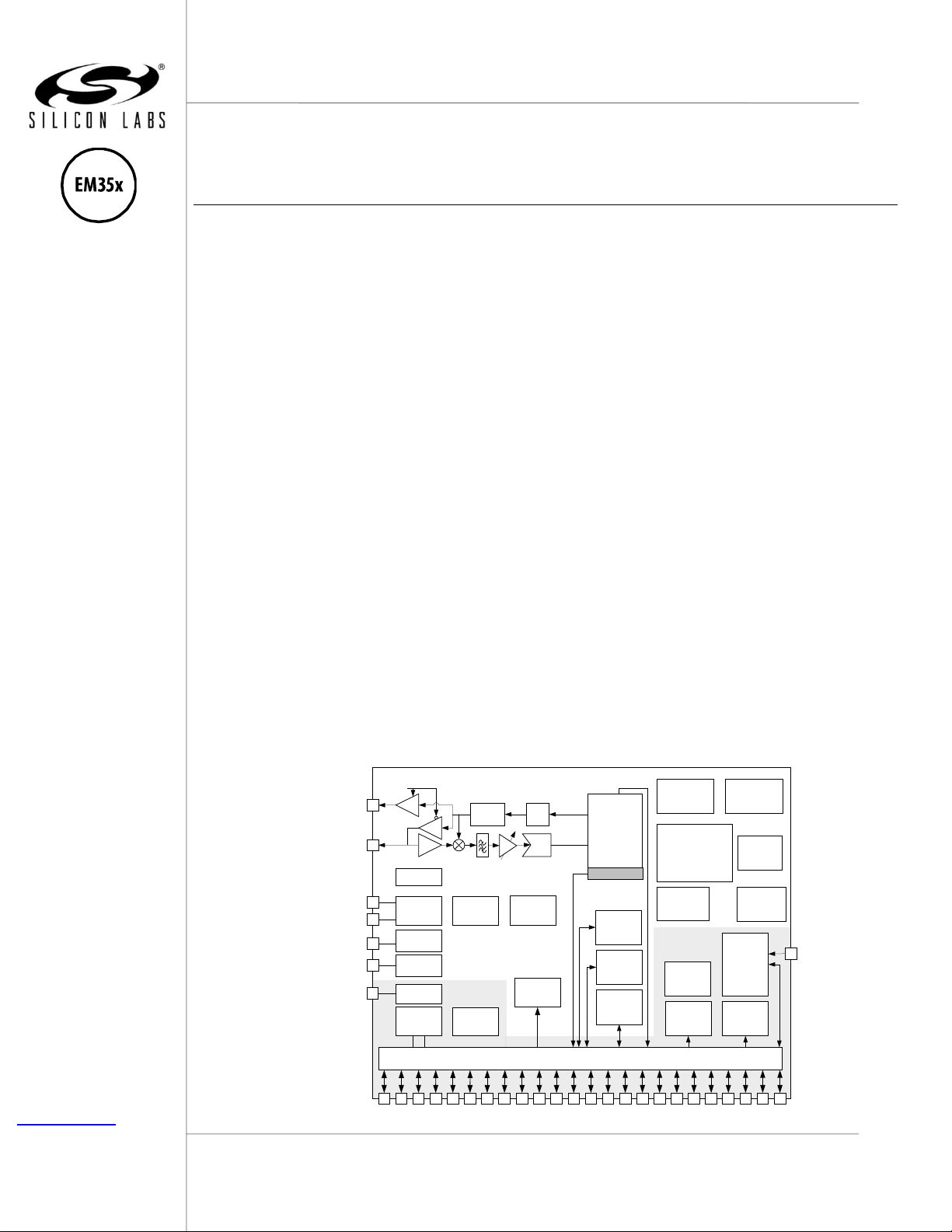

ADC

RF_P,N

Program

Flash

128/192 kB

Data

RAM

12 kB

HF crystal

OSC

LF crystal

OSC

General

Purpose

ADC

Serial

Wire and

JTAG

debug

Internal LF

RC-OSC

GPIO multiplexor switch

Chip

manager

1.8V

Regulator

Bias

2

nd

level

Interrupt

controller

RF_TX_ALT_P,N

OSCA

OSCB

PA[7:0], PB[7:0], PC[7:0]

Encryption

acclerator

IF

Always

Powered

Domain

ARM

®

Cortex

TM

-M3

CPU with NVIC

and MPU

VREG_OUT

Watchdog

PA select

LNA

PA

PA

DAC

MAC

+

Baseband

Sleep

timer

POR

nRESET

General

purpose

timers

GPIO

registers

UART/

SPI/TWI

SYNTH

Internal HF

RC-OSC

TX_ACTIVE

SWCLK,

JTCK

Calibration

ADC

Packet Trace

CPU debug

TPIU/ITM/

FPB/DWT

1.25V

Regulator

VDD_CORE

ADC

RF_P,N

Program

Flash

128/192 kB

Data

RAM

12 kB

HF crystal

OSC

LF crystal

OSC

General

Purpose

ADC

Serial

Wire and

JTAG

debug

Internal LF

RC-OSC

GPIO multiplexor switch

Chip

manager

1.8V

Regulator

Bias

2

nd

level

Interrupt

controller

RF_TX_ALT_P,N

OSCA

OSCB

PA[7:0], PB[7:0], PC[7:0]

Encryption

acclerator

IF

Always

Powered

Domain

ARM

®

Cortex

TM

-M3

CPU with NVIC

and MPU

VREG_OUT

Watchdog

PA select

LNA

PA

PA

DAC

MAC

+

Baseband

Sleep

timer

POR

nRESET

General

purpose

timers

GPIO

registers

UART/

SPI/TWI

SYNTH

Internal HF

RC-OSC

TX_ACTIVE

SWCLK,

JTCK

Calibration

ADC

Packet Trace

CPU debug

TPIU/ITM/

FPB/DWT

1.25V

Regulator

VDD_CORE

EM351 / EM357

High-Performance, Integrated ZigBee/802.15.4 System-on-Chip

Complete System-on-Chip

•

32-bit ARM

®

Cortex-M3 processor

•

2.4 GHz IEEE 802.15.4-2003 transceiver & lower

MAC

•

128 or 192 kB flash, with optional read

protection

•

12 kB RAM memory

•

AES128 encryption accelerator

•

Flexible ADC, UART/SPI/TWI serial

communications, and general purpose timers

•

24 highly configurable GPIOs with Schmitt

trigger inputs

Industry-leading ARM

®

Cortex

-M3 processor

•

Leading 32-bit processing performance

•

Highly efficient Thumb-2 instruction set

•

Operation at 6, 12, or 24 MHz

•

Flexible Nested Vectored Interrupt Controller

Low power consumption, advanced management

•

Rx Current (w/ CPU): 26 mA

•

Tx Current (w/ CPU, +3 dBm TX): 31 mA

•

Low deep sleep current, with retained RAM and

GPIO: 400 nA without/800 nA with sleep timer

•

Low-frequency internal RC oscillator for low-

power sleep timing

•

High-frequency internal RC oscillator for fast

(110 µsec) processor start-up from sleep

Exceptional RF Performance

•

Normal mode link budget up to 103 dB;

configurable up to 110 dB

•

-100 dBm normal RX sensitivity;

configurable to -102 dBm

(1% PER, 20 byte packet)

•

+3 dB normal mode output power;

configurable up to +8 dBm

•

Robust Wi-Fi and Bluetooth coexistence

Innovative network and processor debug

•

Ember InSight port for non-intrusive

packet trace with Ember InSight tools

•

Serial Wire/JTAG interface

•

Standard ARM debug capabilities: Flash

Patch & Breakpoint; Data Watchpoint &

Trace; Instrumentation Trace Macrocell

Application Flexibility

•

Single voltage operation: 2.1-3.6 V

with internal 1.8 V and 1.25 V regulators

•

Optional 32.768 kHz crystal for higher

timer accuracy

•

Low external component count with

single 24 MHz crystal

•

Support for external power amplifier

•

Small 7x7 mm 48-pin QFN package

Silicon Laboratories Inc.

400 West Cesar Chavez

Austin, TX 78701

Tel: 1+(512) 416-8500

Fax: 1+(512) 416-9669

Toll Free: 1+(877) 444-3032

www.silabs.com

120-035X-000M

Final

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件