Datasheet 搜索 > FPGA芯片 > Altera(阿尔特拉) > EP1AGX50CF484C6N 数据手册 > EP1AGX50CF484C6N 数据手册 42/234 页

器件3D模型

器件3D模型¥ 3192.112

EP1AGX50CF484C6N 数据手册 - Altera(阿尔特拉)

制造商:

Altera(阿尔特拉)

分类:

FPGA芯片

封装:

FBGA-484

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

原理图在P8P38P67

封装尺寸在P231

型号编码规则在P231

技术参数、封装参数在P11P12P102P123P124P125P137P138P139P140P141P142

应用领域在P207P208

电气规格在P136

型号编号列表在P123

导航目录

EP1AGX50CF484C6N数据手册

Page:

of 234 Go

若手册格式错乱,请下载阅览PDF原文件

2–36 Chapter 2: Arria GX Architecture

Adaptive Logic Modules

Arria GX Device Handbook, Volume 1 © December 2009 Altera Corporation

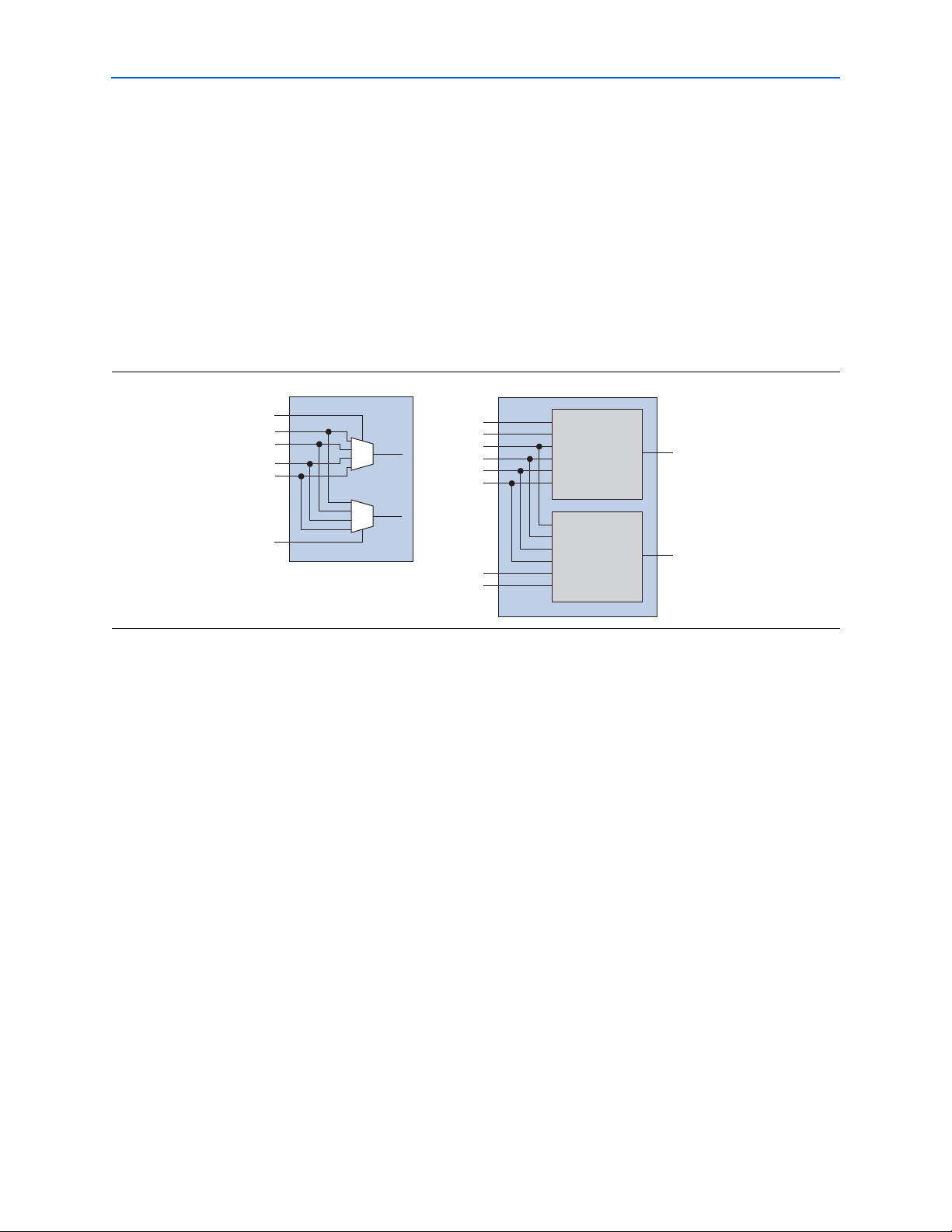

To pack two five-input functions into one ALM, the functions must have at least two

common inputs. The common inputs are dataa and datab. The combination of a

four-input function with a five-input function requires one common input

(either dataa or datab).

To implement two six-input functions in one ALM, four inputs must be shared and

the combinational function must be the same. For example, a 4 × 2 crossbar switch

(two 4-to-1 multiplexers with common inputs and unique select lines) can be

implemented in one ALM, as shown in Figure 2–31. The shared inputs are dataa,

datab, datac, and datad, while the unique select lines are datae0 and dataf0 for

function0, and datae1 and dataf1 for function1. This crossbar switch

consumes four LUTs in a four-input LUT-based architecture.

In a sparsely used device, functions that can be placed into one ALM can be

implemented in separate ALMs. The Quartus II Compiler spreads a design out to

achieve the best possible performance. As a device begins to fill up, the Quartus II

software automatically uses the full potential of the Arria GX ALM. The Quartus II

Compiler automatically searches for functions of common inputs or completely

independent functions to be placed into one ALM and to make efficient use of the

device resources. In addition, you can manually control resource usage by setting

location assignments. Any six-input function can be implemented utilizing inputs

dataa, datab, datac, datad, and either datae0 and dataf0 or datae1 and

dataf1. If datae0 and dataf0 are used, the output is driven to register0,

and/or register0 is bypassed and the data drives out to the interconnect using the

top set of output drivers (refer to Figure 2–32). If datae1 and dataf1 are used, the

output drives to register1 and/or bypasses register1 and drives to the

interconnect using the bottom set of output drivers. The Quartus II Compiler

automatically selects the inputs to the LUT. Asynchronous load data for the register

comes from the datae or dataf input of the ALM. ALMs in normal mode support

register packing.

Figure 2–31. 4 × 2 Crossbar Switch Example

Six-Input

LUT

(Function0)

dataf0

datae0

dataa

datab

datac

Six-Input

LUT

(Function1)

datad

datae1

combout0

combout1

dataf1

inputa

sel0[1..0]

sel1[1..0]

inputb

inputc

inputd

out0

out1

4 ´ 2 Crossbar Switch Implementation in 1 ALM

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件