Datasheet 搜索 > FPGA芯片 > Altera(阿尔特拉) > EP2C8T144I8N 数据手册 > EP2C8T144I8N 数据手册 14/168 页

器件3D模型

器件3D模型¥ 99.451

EP2C8T144I8N 数据手册 - Altera(阿尔特拉)

制造商:

Altera(阿尔特拉)

分类:

FPGA芯片

封装:

TQFP-144

描述:

ALTERA EP2C8T144I8N 芯片, FPGA, CYCLONE II, 8K单元, TQFP144

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

典型应用电路图在P14P16P18

原理图在P14P86

型号编码规则在P167

功能描述在P13

技术参数、封装参数在P63P78P83P84P86P91P93P95P97P99P101P102

应用领域在P105P106P107P108P167

导航目录

EP2C8T144I8N数据手册

Page:

of 168 Go

若手册格式错乱,请下载阅览PDF原文件

2–2 Altera Corporation

Cyclone II Device Handbook, Volume 1 February 2007

Logic Elements

phase-align double data rate (DDR) signals) provide interface support for

external memory devices such as DDR, DDR2, and single data rate (SDR)

SDRAM, and QDRII SRAM devices at up to 167 MHz.

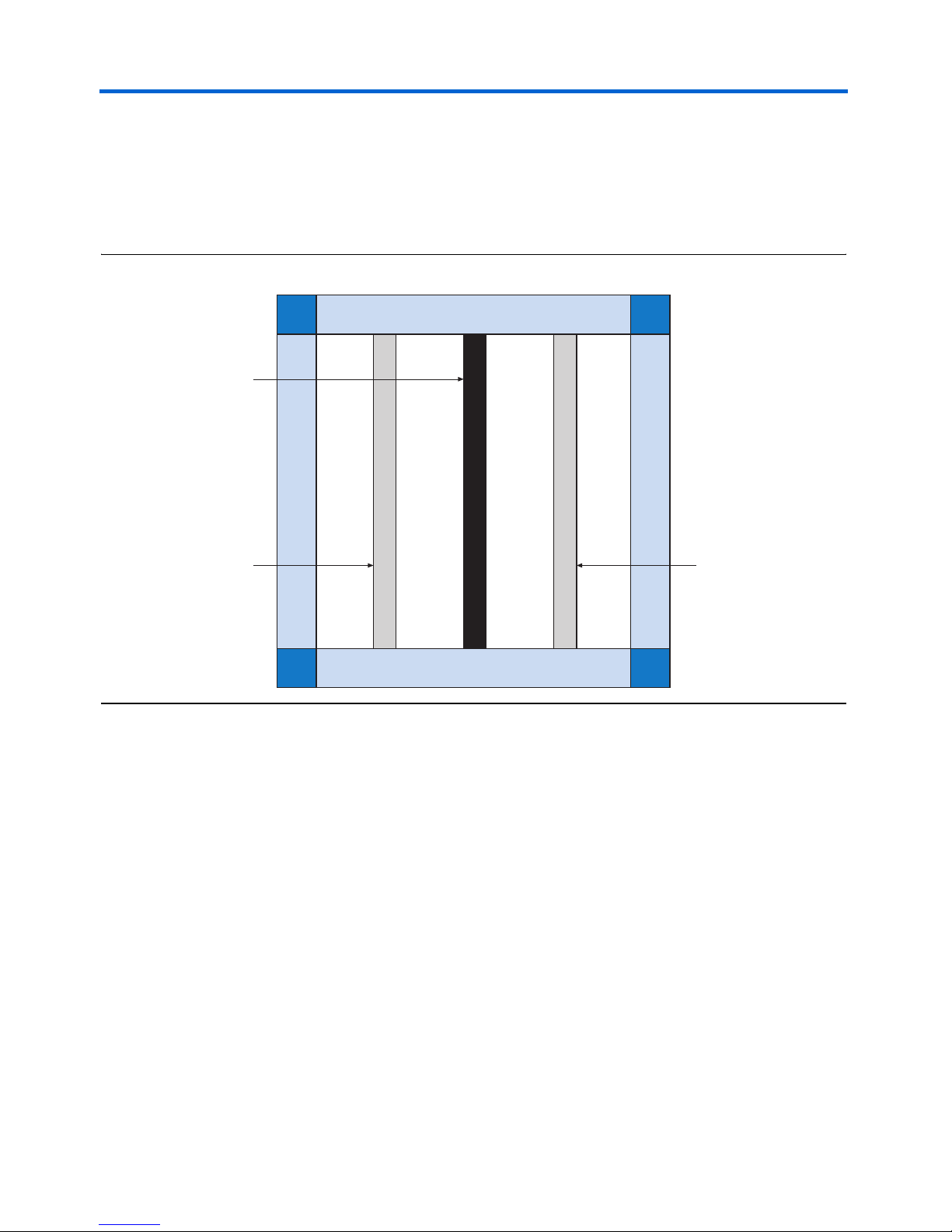

Figure 2–1 shows a diagram of the Cyclone II EP2C20 device.

Figure 2–1. Cyclone II EP2C20 Device Block Diagram

The number of M4K memory blocks, embedded multiplier blocks, PLLs,

rows, and columns vary per device.

Logic Elements

The smallest unit of logic in the Cyclone II architecture, the LE, is compact

and provides advanced features with efficient logic utilization. Each LE

features:

■ A four-input look-up table (LUT), which is a function generator that

can implement any function of four variables

■ A programmable register

■ A carry chain connection

■ A register chain connection

■ The ability to drive all types of interconnects: local, row, column,

register chain, and direct link interconnects

■ Support for register packing

■ Support for register feedback

PLL PLLIOEs

PLL PLLIOEs

IOEs

Logic

Array

Logic

Array

Logic

Array

Logic

Array

IOEs

M4K Block

s

M4K Blocks

Embedded

Multipliers

Downloaded from Elcodis.com electronic components distributor

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件