Datasheet 搜索 > FPGA芯片 > Altera(阿尔特拉) > EP3SE110F1152I4 数据手册 > EP3SE110F1152I4 数据手册 1/332 页

器件3D模型

器件3D模型¥ 1234.745

EP3SE110F1152I4 数据手册 - Altera(阿尔特拉)

制造商:

Altera(阿尔特拉)

分类:

FPGA芯片

封装:

FBGA-1152

描述:

FPGA - 现场可编程门阵列 FPGA - Stratix III 4300 LABs 744 IOs

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

技术参数、封装参数在P1P2P5P6P8P9P10P11P12P13P14P15

电气规格在P1P2P3P4P5P6P7P8P9P10P11P12

导航目录

EP3SE110F1152I4数据手册

Page:

of 332 Go

若手册格式错乱,请下载阅览PDF原文件

© July 2010 Altera Corporation Stratix III Device Handbook, Volume 2

1. Stratix III Device Datasheet: DC and

Switching Characteristics

Electrical Characteristics

This chapter describes the electrical characteristics, switching characteristics, and I/O

timing for Stratix

®

III devices. Electrical characteristics include operating conditions

and power consumption. Switching characteristics include core performance

specifications and periphery performance. A glossary is also included for your

reference.

Operating Conditions

When Stratix III devices are implemented in a system, they are rated according to a set

of defined parameters. To maintain the highest possible performance and reliability of

Stratix III devices, system designers must consider the operating requirements

described in this chapter.

Stratix III devices are offered in both commercial and industrial grades. Commercial

devices are offered in –2 (fastest), –3, –4, and –4L speed grades. Industrial devices are

offered only in –3, –4, and –4L speed grades.

1 In this chapter, a prefix associated with the operating temperature range is attached to

the speed grades; commercial with a “C” prefix and industrial with an “I” prefix. For

example, commercial devices are indicated as C2, C3, C4, and C4L per respective

speed grades. Industrial devices are indicated as I3, I4, and I4L.

Absolute Maximum Ratings

Absolute maximum ratings define the maximum operating conditions for Stratix III

devices. The values are based on experiments conducted with the device and

theoretical modeling of breakdown and damage mechanisms. The functional

operation of the device is not implied at these conditions. Conditions beyond those

listed in Table 1–1 may cause permanent damage to the device. Additionally, device

operation at the absolute maximum ratings for extended periods may have adverse

effects on the device.

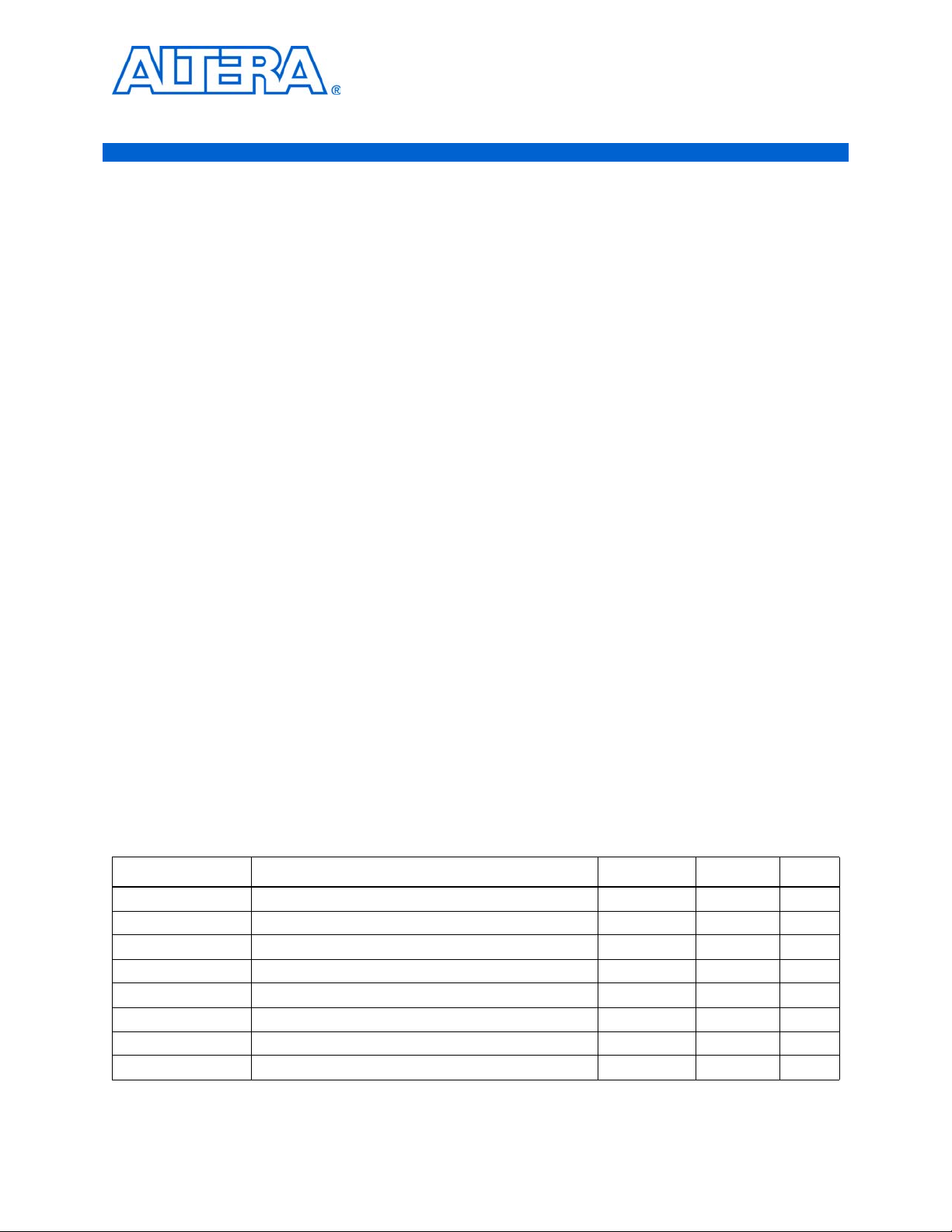

Table 1–1. Absolute Maximum Ratings for Stratix III Devices (Note 1) (Part 1 of 2)

Symbol Parameter Minimum Maximum Unit

V

CCL

Selectable core voltage power supply -0.5 1.65 V

V

CC

I/O registers power supply -0.5 1.65 V

V

CCD_PLL

Phase-locked loop (PLL) digital power supply -0.5 1.65 V

V

CCA_PLL

PLL analog power supply -0.5 3.75 V

V

CCPT

Programmable power technology power supply -0.5 3.75 V

V

CCPGM

Configuration pins power supply -0.5 3.9 V

V

CCPD

I/O pre-driver power supply -0.5 3.9 V

V

CCIO

I/O power supply -0.5 3.9 V

SIII52001-2.3

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件