Datasheet 搜索 > Intel(英特尔) > EP4CE6E22I8LN 数据手册 > EP4CE6E22I8LN 数据手册 254/490 页

器件3D模型

器件3D模型¥ 130.242

EP4CE6E22I8LN 数据手册 - Intel(英特尔)

制造商:

Intel(英特尔)

封装:

LQFP-144

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P72P149P213P249P265P281Hot

典型应用电路图在P9P17P18P22P29P30P31P32P33P34P233

原理图在P41P82P83P234P250P254P285P286P290P293P295P297

型号编码规则在P26

封装信息在P26P153

功能描述在P233

技术参数、封装参数在P63P103P153P265P266P448P454P457P458P459P460P461

应用领域在P93P249

电气规格在P447

导航目录

EP4CE6E22I8LN数据手册

Page:

of 490 Go

若手册格式错乱,请下载阅览PDF原文件

9–8 Chapter 9: SEU Mitigation in Cyclone IV Devices

Software Support

Cyclone IV Device Handbook, May 2013 Altera Corporation

Volume 1

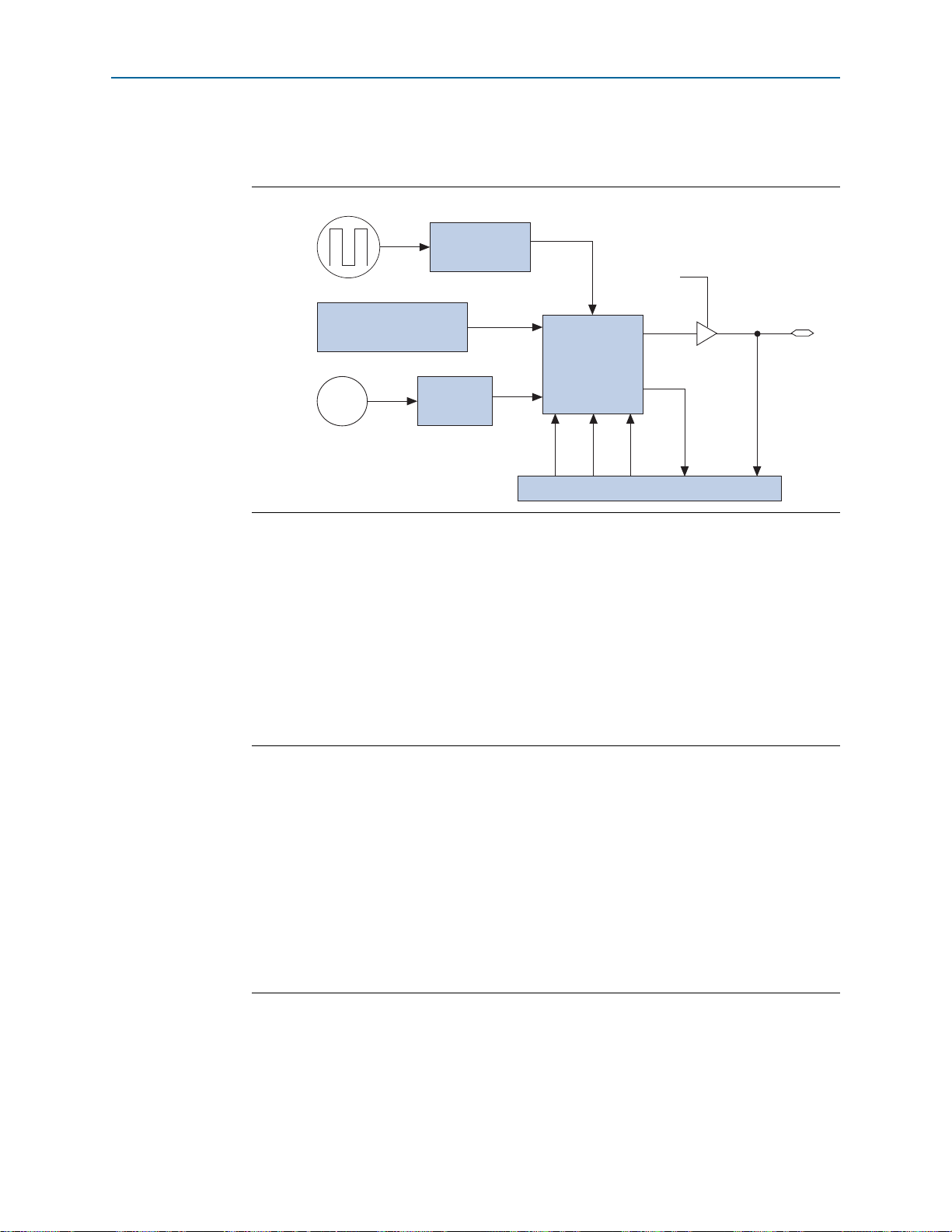

Figure 9–3 shows the error detection block diagram in FPGA devices and shows the

interface that the WYSIWYG atom enables in your design.

1 The user logic is affected by the soft error failure, so reading out the 32-bit CRC

signature through the

regout

should not be relied upon to detect a soft error. You

should rely on the

CRC_ERROR

output signal itself, because this

CRC_ERROR

output

signal cannot be affected by a soft error.

To enable the

cycloneiv_crcblock

WYSIWYG atom, you must name the atom for

each Cyclone IV device accordingly.

Example 9–1 shows an example of how to define the input and output ports of a

WYSIWYG atom in a Cyclone IV device.

Figure 9–3. Error Detection Block Diagram

Clock Divider

(1 to 256 Factor)

Pre-Computed CRC

(Saved in the Option Register)

CRC

Computation

Error Detection

Logic

SRAM

Bits

CRC_ERROR

(Shown in BIDIR Mode)

V

CC

Logic Array

CLK

SHIFTNLD

LDSRC

REGOUT

CRC_ERROR

80 MHz Internal Chip Oscillator

Example 9–1. Error Detection Block Diagram

cycloneiv_crcblock<crcblock_name>

(

.clk(<clock source>),

.shiftnld(<shiftnld source>),

.ldsrc(<ldsrc source>),

.crcerror(<crcerror out destination>),

.regout(<output destination>),

);

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件