Datasheet 搜索 > Intel(英特尔) > EP4CE6E22I8LN 数据手册 > EP4CE6E22I8LN 数据手册 303/490 页

器件3D模型

器件3D模型¥ 130.242

EP4CE6E22I8LN 数据手册 - Intel(英特尔)

制造商:

Intel(英特尔)

封装:

LQFP-144

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P72P149P213P249P265P281Hot

典型应用电路图在P9P17P18P22P29P30P31P32P33P34P233

原理图在P41P82P83P234P250P254P285P286P290P293P295P297

型号编码规则在P26

封装信息在P26P153

功能描述在P233

技术参数、封装参数在P63P103P153P265P266P448P454P457P458P459P460P461

应用领域在P93P249

电气规格在P447

导航目录

EP4CE6E22I8LN数据手册

Page:

of 490 Go

若手册格式错乱,请下载阅览PDF原文件

Chapter 1: Cyclone IV Transceivers Architecture 1–23

Receiver Channel Datapath

February 2015 Altera Corporation Cyclone IV Device Handbook,

Volume 2

Rate Match FIFO

In asynchronous systems, the upstream transmitter and local receiver can be clocked

with independent reference clocks. Frequency differences in the order of a few

hundred ppm can corrupt the data when latching from the recovered clock domain

(the same clock domain as the upstream transmitter reference clock) to the local

receiver reference clock domain. Figure 1–21 shows the rate match FIFO block

diagram.

The rate match FIFO compensates for small clock frequency differences of up to

±300 ppm (600 ppm total) between the upstream transmitter and the local receiver

clocks by performing the following functions:

■ Insert skip symbols when the local receiver reference clock frequency is greater

than the upstream transmitter reference clock frequency

■ Delete skip symbols when the local receiver reference clock frequency is less than

the upstream transmitter reference clock frequency

The 20-word deep rate match FIFO and logics control insertion and deletion of skip

symbols, depending on the ppm difference. The operation begins after the word

aligner synchronization status (

rx_syncstatus

) is asserted.

1 Rate match FIFO is only supported with 8B/10B encoded data and the word aligner

in automatic synchronization state machine mode.

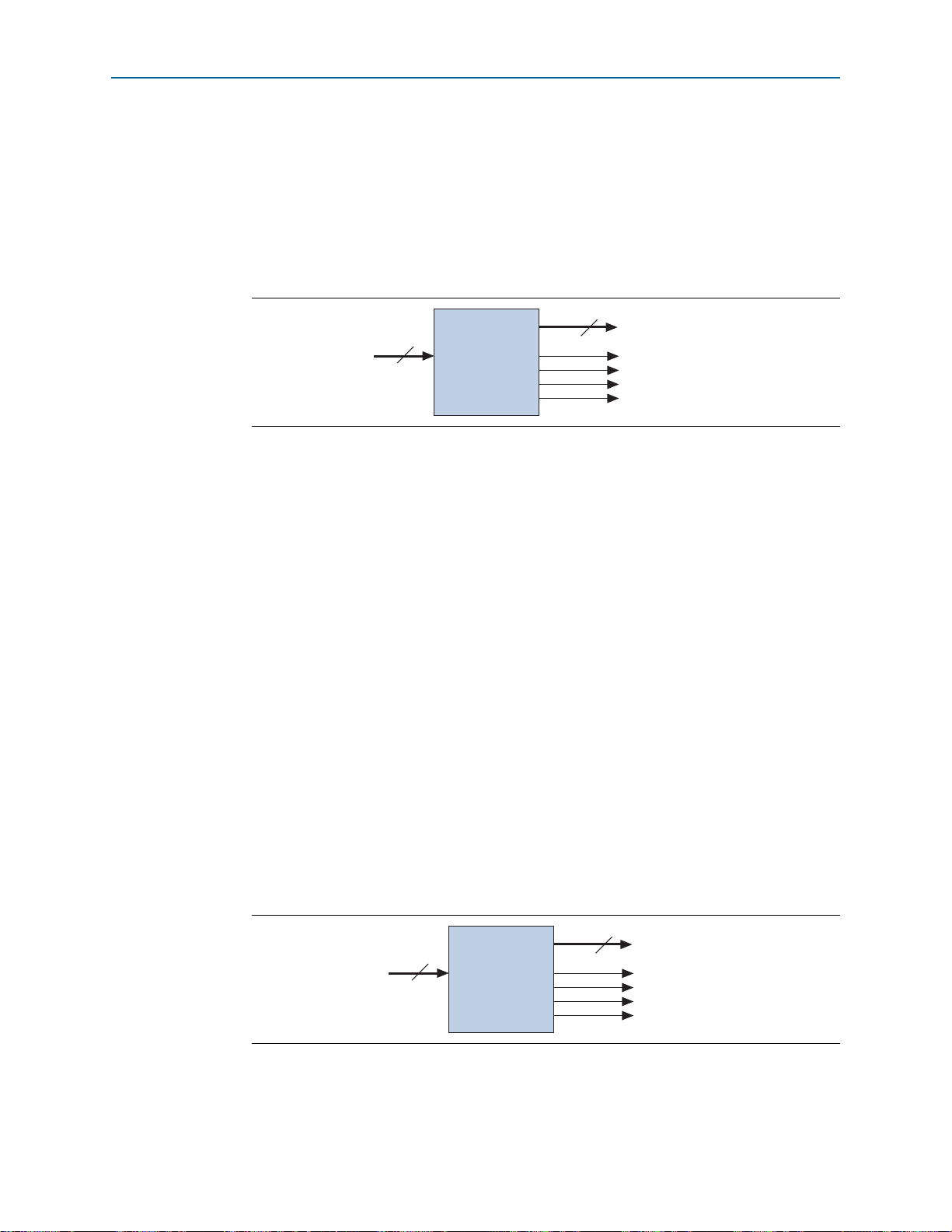

8B/10B Decoder

The 8B/10B decoder receives 10-bit data and decodes it into an 8-bit data and a 1-bit

control identifier. The decoder is compliant with Clause 36 of the IEEE 802.3

specification.

Figure 1–22 shows the 8B/10B decoder block diagram.

Figure 1–21. Rate Match FIFO Block Diagram

Rate Match

FIFO

(20-word deep)

10

rx_rmfifodatainserted

rx_rmfifodatadeleted

rx_fifoempty

rx_rmfifofull

10

Figure 1–22. 8B/10B Decoder Block Diagram

8B/10B Decoder

8

rx_ctrldetect

rx_errdetect

rx_disperr

rx_runningdisp

10

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件