Datasheet 搜索 > 时钟信号器件 > Integrated Device Technology(艾迪悌) > ICS950201AGLF 数据手册 > ICS950201AGLF 数据手册 1/15 页

器件3D模型

器件3D模型¥ 0

ICS950201AGLF 数据手册 - Integrated Device Technology(艾迪悌)

制造商:

Integrated Device Technology(艾迪悌)

分类:

时钟信号器件

封装:

TSSOP-56

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

ICS950201AGLF数据手册

Page:

of 15 Go

若手册格式错乱,请下载阅览PDF原文件

ICS950201

IDT

TM

Programmable Timing Control Hub

TM

for P4

TM

460J—01/25/10

Programmable Timing Control Hub

TM

for P4

TM

1

DATASHEET

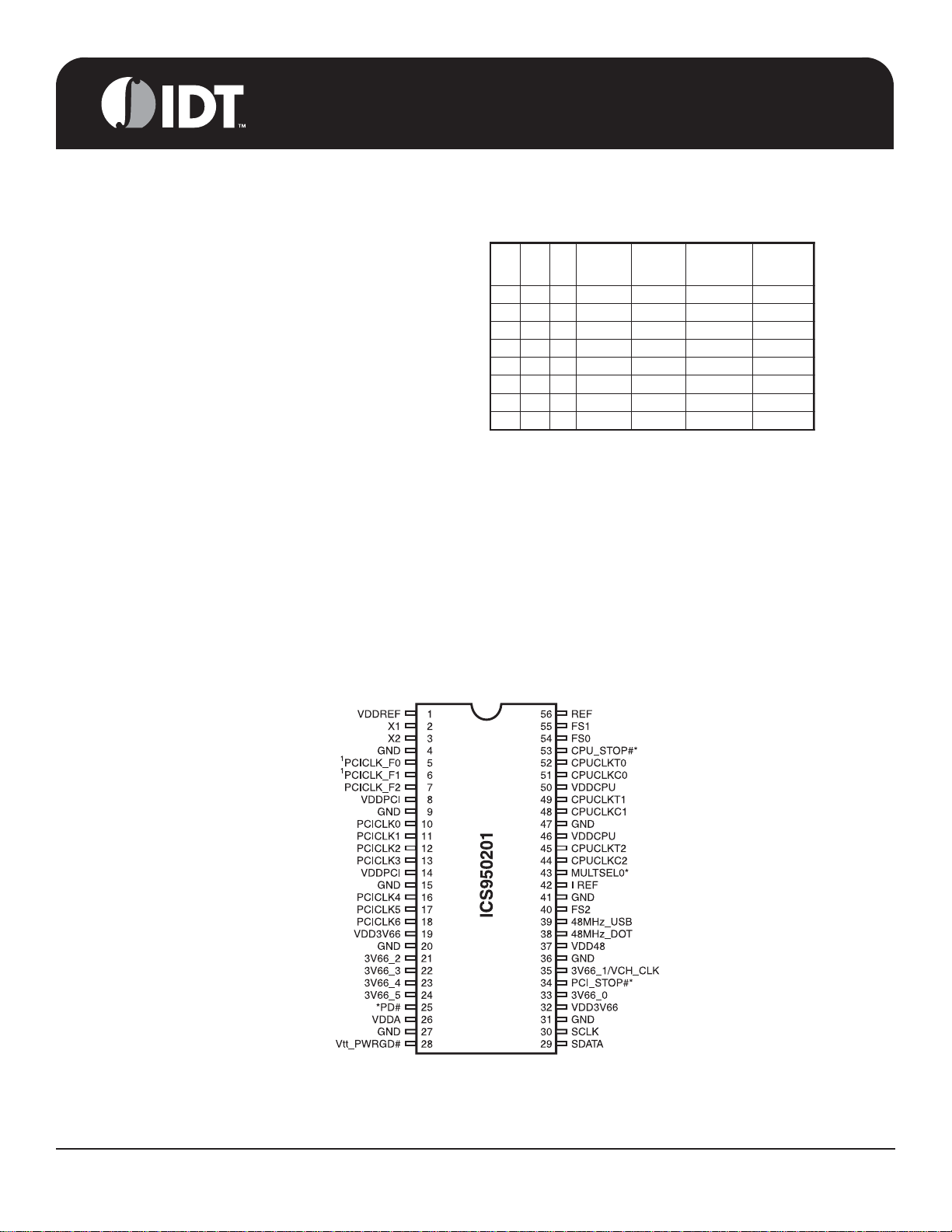

Pin Configuration

Recommended Application:

CK-408 clock for Intel

®

845 chipset with P4 processor.

Output Features:

• 3 Differential CPU Clock Pairs @ 3.3V

• 7 PCI (3.3V) @ 33.3MHz

• 3 PCI_F (3.3V) @ 33.3MHz

• 1 USB (3.3V) @ 48MHz

• 1 DOT (3.3V) @ 48MHz

• 1 REF (3.3V) @ 14.318MHz

• 5 3V66 (3.3V) @ 66.6MHz

• 1 VCH/3V66 (3.3V) @ 48MHz or 66.6MHz

Features:

• Supports spread spectrum modulation,

down spread 0 to -0.5%.

• Efficient power management scheme through PD#,

CPU_STOP# and PCI_STOP#.

• Uses external 14.318MHz crystal

• Stop clocks and functional control available through

I

2

C interface.

Key Specifications:

• CPU Output Jitter <150ps

• 3V66 Output Jitter <250ps

• CPU Output Skew <100ps, programmable over 800 ps

with groups CPU0,1 and CPU2.

56-Pin SSOP & TSSOP

* These inputs have 150K internal pull-up resistor to VDD.

Frequency Table

2SF1SF0SF

UPC

)zHM(

66V3

)zHM(

]0:2[ffuB66

]2:4[66V3

)zHM(

F_ICP

ICP

)zHM(

000 66.6666.6666.6633.33

001 00.00166.6666.6633.33

010 00.0

0266.6666.6633.33

011 33.33166.6666.6633.33

diM00 etatsirTetatsirTetatsirTetatsirT

diM01 2/KLCT4/KLCT4/KLCT8/KLCT

diM10 devreseRdevres

eRdevreseRdevreseR

diM11 devreseRdevreseRdevreseRdevreseR

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件