Datasheet 搜索 > Integrated Device Technology(艾迪悌) > IDT7006S35F 数据手册 > IDT7006S35F 数据手册 1/20 页

¥ 0

IDT7006S35F 数据手册 - Integrated Device Technology(艾迪悌)

制造商:

Integrated Device Technology(艾迪悌)

描述:

高速16K ×8双端口静态RAM HIGH-SPEED 16K x 8 DUAL-PORT STATIC RAM

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

IDT7006S35F数据手册

Page:

of 20 Go

若手册格式错乱,请下载阅览PDF原文件

I/O

Control

Address

Decoder

MEMORY

ARRAY

ARBITRATION

INTERRUPT

SEMAPHORE

LOGIC

Address

Decoder

I/O

Control

R/

W

L

CE

L

OE

L

BUSY

L

A

13L

A

0L

2739 drw 01

I/O

0L

- I/O

7L

CE

L

OE

L

R/

W

L

SEM

L

INT

L

M/

S

BUSY

R

I/O

0R

-I/O

7R

A

13R

A

0R

SEM

R

INT

R

CE

R

OE

R

(2)

(1,2)

(1,2)

(2)

R/

W

R

CE

R

OE

R

R/

W

R

14

14

Integrated Device Technology, Inc.

MILITARY AND COMMERCIAL TEMPERATURE RANGES OCTOBER 1996

©1996 Integrated Device Technology, Inc. DSC-2739/5

IDT7006S/L

HIGH-SPEED

16K x 8 DUAL-PORT

STATIC RAM

FEATURES:

• True Dual-Ported memory cells which allow simulta-

neous access of the same memory location

• High-speed access

— Military: 20/25/35/55/70ns (max.)

— Commercial: 15/17/20/25/35/55ns (max.)

• Low-power operation

— IDT7006S

Active: 750mW (typ.)

Standby: 5mW (typ.)

— IDT7006L

Active: 750mW (typ.)

Standby: 1mW (typ.)

• IDT7006 easily expands data bus width to 16 bits or

more using the Master/Slave select when cascading

more than one device

•M/

S

= H for

BUSY

output flag on Master,

M/

S

= L for

BUSY

input on Slave

• Busy and Interrupt Flags

• On-chip port arbitration logic

• Full on-chip hardware support of semaphore signaling

between ports

• Fully asynchronous operation from either port

• Devices are capable of withstanding greater than 2001V

electrostatic discharge

• Battery backup operation—2V data retention

• TTL-compatible, single 5V (±10%) power supply

• Available in a 68-pin PGA, a 68-pin quad flatpack, a 68-

pin PLCC, and a 64-pin TQFP

• Industrial temperature range (–40°C to +85°C) is avail-

able, tested to military electrical specifications

DESCRIPTION:

The IDT7006 is a high-speed 16K x 8 Dual-Port Static

RAM. The IDT7006 is designed to be used as a stand-alone

Dual-Port RAM or as a combination MASTER/SLAVE Dual-

Port RAM for 16-bit-or-more word systems. Using the IDT

MASTER/SLAVE Dual-Port RAM approach in 16-bit or wider

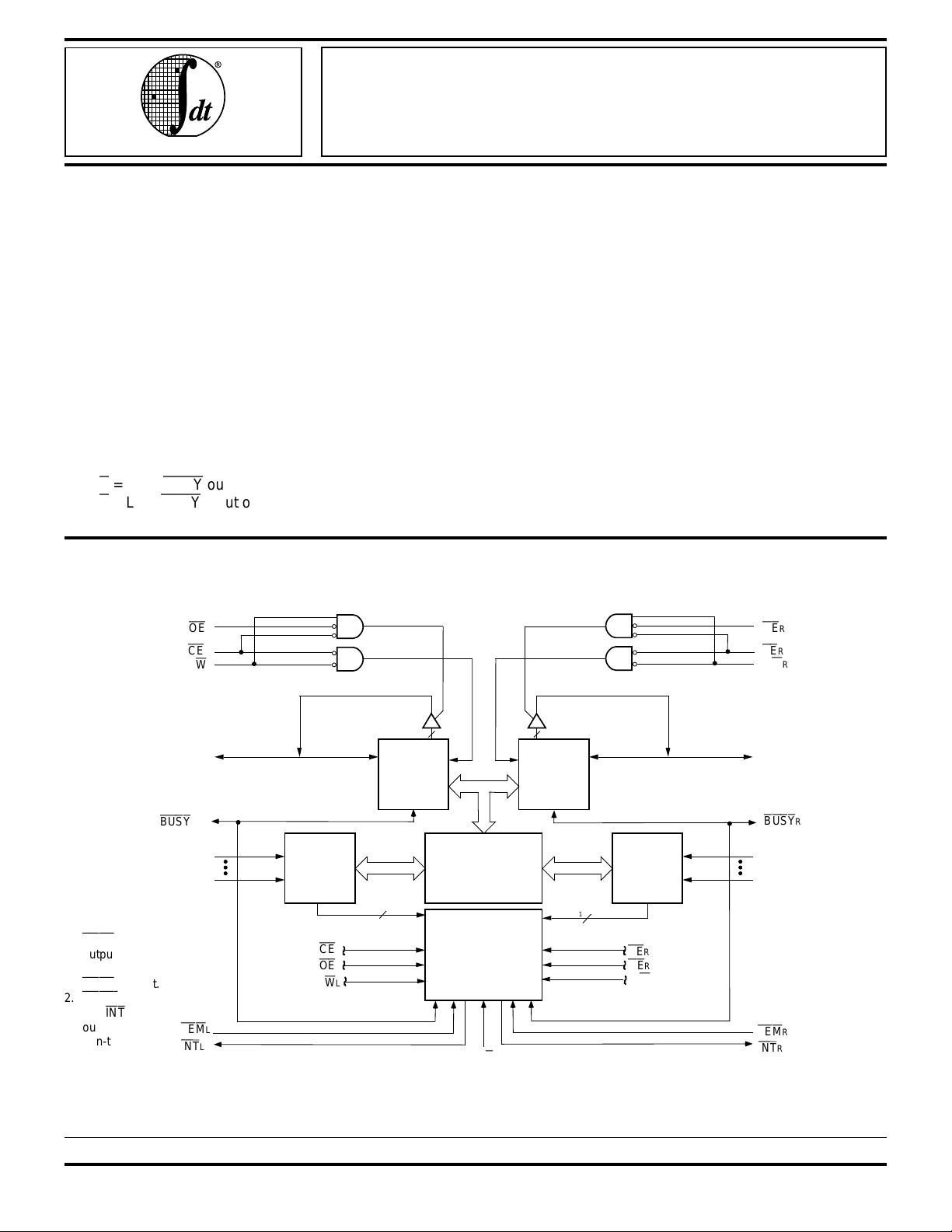

FUNCTIONAL BLOCK DIAGRAM

1

NOTES:

1. (MASTER):

BUSY

is

output;

(SLAVE):

BUSY

is input.

2.

BUSY

outputs

and

INT

outputs are

non-tri-stated

push-pull.

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

6.07

For latest information contact IDT’s web site at www.idt.com or fax-on-demand at 408-492-8391.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件