Datasheet 搜索 > TVS二极管 > NXP(恩智浦) > IP4220CZ6 数据手册 > IP4220CZ6 数据手册 3/9 页

¥ 0.937

IP4220CZ6 数据手册 - NXP(恩智浦)

制造商:

NXP(恩智浦)

分类:

TVS二极管

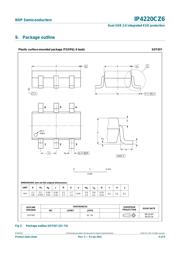

封装:

SC-74

描述:

双USB 2.0集成ESD保护符合IEC 61000-4-2 4级 Dual USB 2.0 Integrated ESD protection to IEC 61000-4-2 level 4

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

IP4220CZ6数据手册

Page:

of 9 Go

若手册格式错乱,请下载阅览PDF原文件

IP4220CZ6 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Product data sheet Rev. 5 — 8 July 2011 3 of 9

NXP Semiconductors

IP4220CZ6

Dual USB 2.0 integrated ESD protection

7. Characteristics

[1] Pins 1, 3, 4 and 6.

[2] Pins 1, 3, 4 and 6 to ground.

[3] Pin 5 to pin 2.

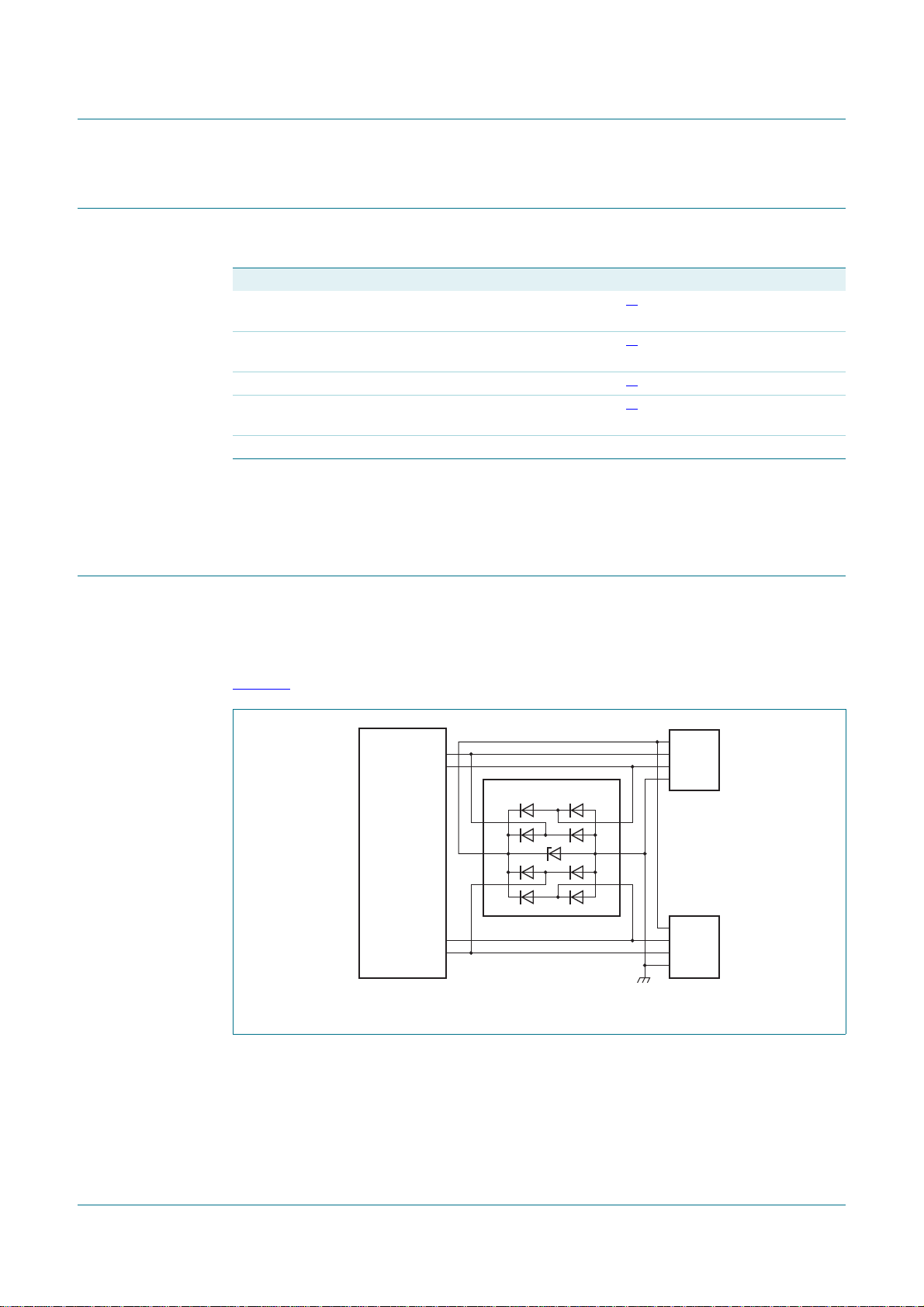

8. Application information

8.1 Universal serial bus 2.0 protection

The device is optimized to protect, for example, two USB 2.0 ports from ESD. Each device

can protect both USB data lines and the V

BUS

supply line. A typical application is shown in

Figure 1

.

Table 6. Characteristics

T

amb

=25

C; unless otherwise specified.

Symbol Parameter Conditions Min Typ Max Unit

C

(I/O-GND)

input/output to

ground capacitance

V

I

=0V; f=1MHz;

V

P

=3V

[1]

-1.0-pF

C

(zd-GND)

Zener diode to

ground capacitance

V

I

=0V; f=1MHz;

V

P

=3V

[3]

-40-pF

I

RM

reverse leakage current V

I

=3V

[2]

- - 100 nA

V

BRzd

Zener diode breakdown

voltage

I=1mA

[3]

6- 9V

V

F

forward voltage - 0.7 - V

Fig 1. Typical application of IP4220CZ6

018aaa143

4

USB 2.0

IEEE1394

CONTROLLER

5

6

3

2

1

V

BUS

D+

D–

GND

V

BUS

D+

D–

GND

IP4220CZ6

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件