Datasheet 搜索 > 微控制器 > TI(德州仪器) > LM3S6965-IQC50-A2T 数据手册 > LM3S6965-IQC50-A2T 数据手册 336/761 页

器件3D模型

器件3D模型¥ 249.791

LM3S6965-IQC50-A2T 数据手册 - TI(德州仪器)

制造商:

TI(德州仪器)

分类:

微控制器

封装:

LQFP-100

描述:

的Stellaris LM3S6965微控制器 Stellaris LM3S6965 Microcontroller

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P160P172P336P396P433P476P514P551P599P612P650Hot

典型应用电路图在P47P610

原理图在P44P45P54P55P56P160P240P260P293P335P372P395

封装尺寸在P52P749P750P752P753P754P756P757P759P760

型号编码规则在P747

标记信息在P747P757P758

封装信息在P747P751P752P756P757P758P759P760

功能描述在P95P161P172P241P260P292P336P372P397P434P476P515

技术参数、封装参数在P699P701P702P703P705

应用领域在P44P58P179P761

电气规格在P52P700P702P704P706P708P710P712P714P716

导航目录

LM3S6965-IQC50-A2T数据手册

Page:

of 761 Go

若手册格式错乱,请下载阅览PDF原文件

9.2 Signal Description

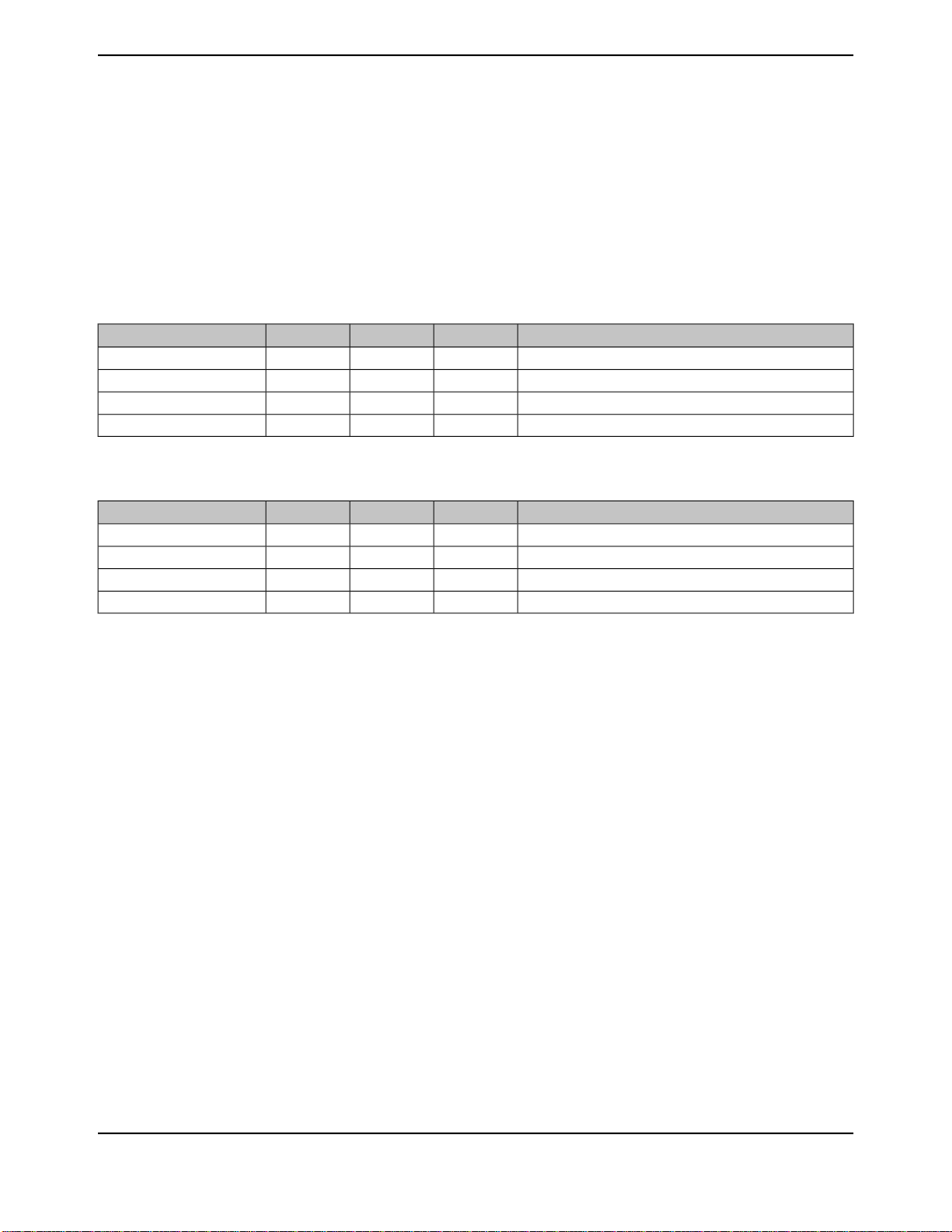

Table 9-2 on page 336 and Table 9-3 on page 336 list the external signals of the GP Timer module

and describe the function of each. The GP Timer signals are alternate functions for some GPIO

signals and default to be GPIO signals at reset. The column in the table below titled "Pin Assignment"

lists the possible GPIO pin placements for these GP Timer signals. The AFSEL bit in the GPIO

Alternate Function Select (GPIOAFSEL) register (page 309) should be set to choose the GP Timer

function. For more information on configuring GPIOs, see “General-Purpose Input/Outputs

(GPIOs)” on page 287.

Table 9-2. General-Purpose Timers Signals (100LQFP)

DescriptionBuffer Type

a

Pin TypePin NumberPin Name

Capture/Compare/PWM 0.TTLI/O95CCP0

Capture/Compare/PWM 1.TTLI/O100CCP1

Capture/Compare/PWM 2.TTLI/O96CCP2

Capture/Compare/PWM 3.TTLI/O23CCP3

a. The TTL designation indicates the pin has TTL-compatible voltage levels.

Table 9-3. General-Purpose Timers Signals (108BGA)

DescriptionBuffer Type

a

Pin TypePin NumberPin Name

Capture/Compare/PWM 0.TTLI/OE1CCP0

Capture/Compare/PWM 1.TTLI/OF1CCP1

Capture/Compare/PWM 2.TTLI/OE2CCP2

Capture/Compare/PWM 3.TTLI/OM2CCP3

a. The TTL designation indicates the pin has TTL-compatible voltage levels.

9.3 Functional Description

The main components of each GPTM block are two free-running 16-bit up/down counters (referred

to as TimerA and TimerB), two 16-bit match registers, two prescaler match registers, and two 16-bit

load/initialization registers and their associated control functions. The exact functionality of each

GPTM is controlled by software and configured through the register interface.

Software configures the GPTM using the GPTM Configuration (GPTMCFG) register (see page 347),

the GPTM TimerA Mode (GPTMTAMR) register (see page 348), and the GPTM TimerB Mode

(GPTMTBMR) register (see page 350). When in one of the 32-bit modes, the timer can only act as

a 32-bit timer. However, when configured in 16-bit mode, the GPTM can have its two 16-bit timers

configured in any combination of the 16-bit modes.

9.3.1 GPTM Reset Conditions

After reset has been applied to the GPTM module, the module is in an inactive state, and all control

registers are cleared and in their default states. Counters TimerA and TimerB are initialized to

0xFFFF, along with their corresponding load registers: the GPTM TimerA Interval Load

(GPTMTAILR) register (see page 361) and the GPTM TimerB Interval Load (GPTMTBILR) register

(see page 362). The prescale counters are initialized to 0x00: the GPTM TimerA Prescale

(GPTMTAPR) register (see page 365) and the GPTM TimerB Prescale (GPTMTBPR) register (see

page 366).

July 15, 2014336

Texas Instruments-Production Data

General-Purpose Timers

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件