Datasheet 搜索 > 逻辑控制器 > ON Semiconductor(安森美) > MC74HC161ADR2G 数据手册 > MC74HC161ADR2G 数据手册 5/16 页

器件3D模型

器件3D模型¥ 1.118

MC74HC161ADR2G 数据手册 - ON Semiconductor(安森美)

制造商:

ON Semiconductor(安森美)

分类:

逻辑控制器

封装:

SOIC-16

描述:

预置计数器高性能硅栅CMOS Presettable Counters High−Performance Silicon−Gate CMOS

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

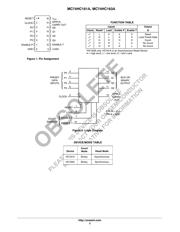

引脚图在P2Hot

典型应用电路图在P2P12P13

封装尺寸在P14P15P16

型号编码规则在P1P13P16

标记信息在P1

封装信息在P13

功能描述在P7

技术参数、封装参数在P13

应用领域在P5P12P13

电气规格在P4P5

导航目录

MC74HC161ADR2G数据手册

Page:

of 16 Go

若手册格式错乱,请下载阅览PDF原文件

MC74HC161A, MC74HC163A

http://onsemi.com

5

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

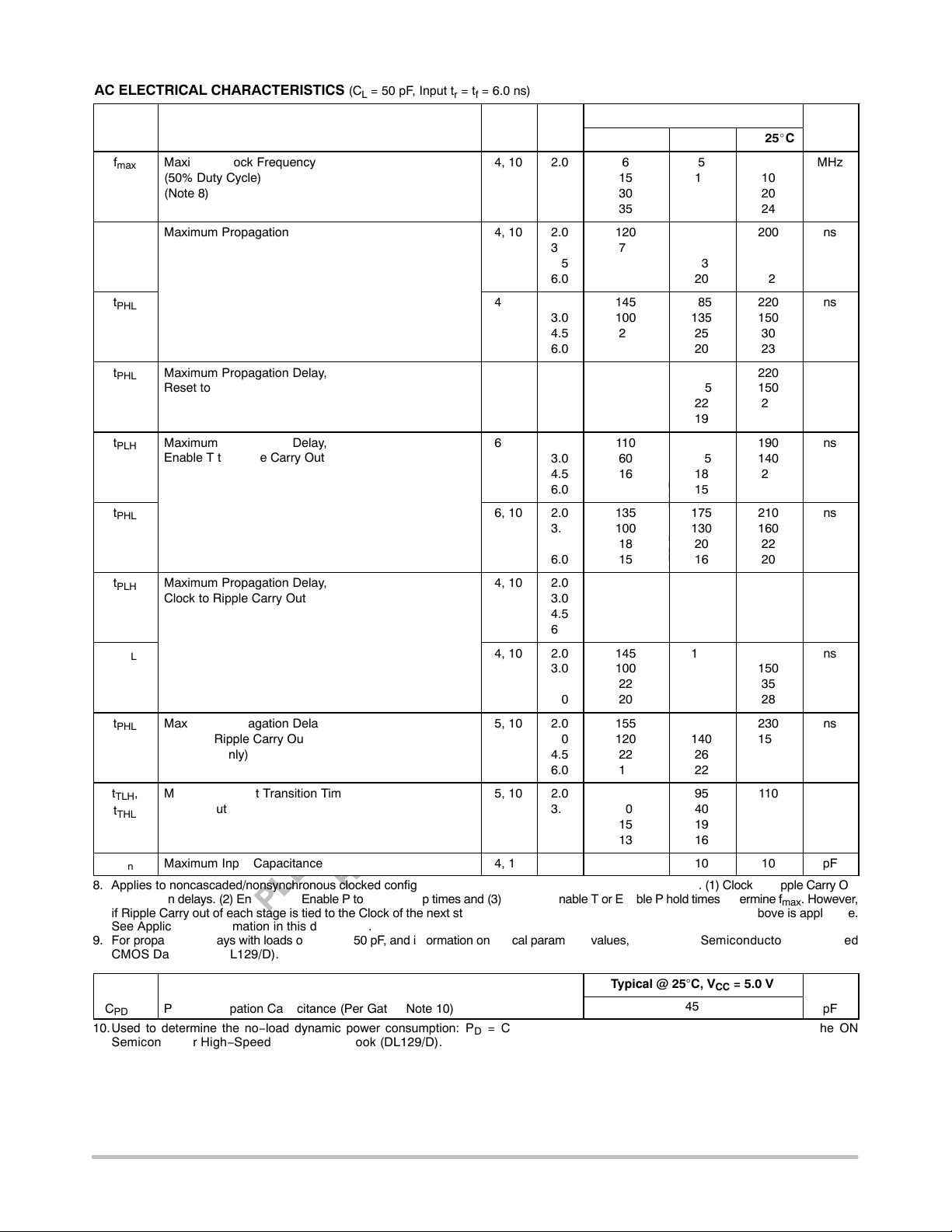

AC ELECTRICAL CHARACTERISTICS (C

L

= 50 pF, Input t

r

= t

f

= 6.0 ns)

ÎÎÎÎ

Î

ÎÎ

Î

ÎÎÎÎ

Symbol

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Parameter

ÎÎÎ

Î

Î

Î

ÎÎÎ

Figure

ÎÎÎ

Î

Î

Î

ÎÎÎ

V

CC

V

ÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎ

Guaranteed Limit

ÎÎÎ

Î

Î

Î

ÎÎÎ

Unit

ÎÎÎÎ

ÎÎÎÎ

– 55 to 25_C

ÎÎÎ

ÎÎÎ

v 85_C

ÎÎÎÎ

ÎÎÎÎ

v 125_C

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

f

max

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Maximum Clock Frequency

(50% Duty Cycle)

(Note 8)

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

4, 10

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

2.0

3.0

4.5

6.0

ÎÎÎÎ

Î

ÎÎÎ

Î

ÎÎÎ

ÎÎÎÎ

6

15

30

35

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

5

12

24

28

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

4

10

20

24

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

MHz

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

t

PLH

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Maximum Propagation Delay,

Clock to Q

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

4, 10

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

2.0

3.0

4.5

6.0

ÎÎÎÎ

Î

ÎÎÎ

Î

ÎÎÎ

ÎÎÎÎ

120

75

20

16

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

160

120

23

20

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

200

150

28

22

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

ns

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

t

PHL

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

4, 10

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

2.0

3.0

4.5

6.0

ÎÎÎÎ

Î

ÎÎÎ

Î

ÎÎÎ

ÎÎÎÎ

145

100

22

18

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

185

135

25

20

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

220

150

30

23

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

ns

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

t

PHL

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Maximum Propagation Delay,

Reset to Q (HC161A Only)

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

5, 10

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

2.0

3.0

4.5

6.0

ÎÎÎÎ

Î

ÎÎÎ

Î

ÎÎÎ

ÎÎÎÎ

145

100

20

17

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

185

135

22

19

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

220

150

25

21

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

ns

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

t

PLH

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Maximum Propagation Delay,

Enable T to Ripple Carry Out

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

6, 10

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

2.0

3.0

4.5

6.0

ÎÎÎÎ

Î

ÎÎÎ

Î

ÎÎÎ

ÎÎÎÎ

110

60

16

14

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

150

115

18

15

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

190

140

20

17

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

ns

ÎÎÎÎ

Î

ÎÎ

Î

ÎÎÎÎ

t

PHL

ÎÎÎ

Î

Î

Î

ÎÎÎ

6, 10

ÎÎÎ

Î

Î

Î

ÎÎÎ

2.0

3.0

4.5

6.0

ÎÎÎÎ

Î

ÎÎÎ

ÎÎÎÎ

135

100

18

15

ÎÎÎ

Î

Î

Î

ÎÎÎ

175

130

20

16

ÎÎÎÎ

Î

ÎÎ

Î

ÎÎÎÎ

210

160

22

20

ÎÎÎ

Î

Î

Î

ÎÎÎ

ns

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

t

PLH

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Maximum Propagation Delay,

Clock to Ripple Carry Out

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

4, 10

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

2.0

3.0

4.5

6.0

ÎÎÎÎ

Î

ÎÎÎ

Î

ÎÎÎ

ÎÎÎÎ

120

75

22

18

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

160

135

27

22

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

200

150

30

25

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

ns

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

t

PHL

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

4, 10

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

2.0

3.0

4.5

6.0

ÎÎÎÎ

Î

ÎÎÎ

Î

ÎÎÎ

ÎÎÎÎ

145

100

22

20

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

185

135

28

24

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

220

150

35

28

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

ns

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

t

PHL

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Maximum Propagation Delay,

Reset to Ripple Carry Out

(HC161A Only)

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

5, 10

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

2.0

3.0

4.5

6.0

ÎÎÎÎ

Î

ÎÎÎ

Î

ÎÎÎ

ÎÎÎÎ

155

120

22

18

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

190

140

26

22

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

230

155

30

25

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

ns

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

t

TLH

,

t

THL

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎ

Î

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Maximum Output Transition Time,

Any Output

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

5, 10

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

2.0

3.0

4.5

6.0

ÎÎÎÎ

Î

ÎÎÎ

Î

ÎÎÎ

ÎÎÎÎ

75

30

15

13

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

95

40

19

16

ÎÎÎÎ

Î

ÎÎ

Î

Î

ÎÎ

Î

ÎÎÎÎ

110

55

22

19

ÎÎÎ

Î

Î

Î

Î

Î

Î

ÎÎÎ

ns

ÎÎÎÎ

ÎÎÎÎ

C

in

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

Maximum Input Capacitance

ÎÎÎ

ÎÎÎ

4, 10

ÎÎÎ

ÎÎÎ

−

ÎÎÎÎ

ÎÎÎÎ

10

ÎÎÎ

ÎÎÎ

10

ÎÎÎÎ

ÎÎÎÎ

10

ÎÎÎ

ÎÎÎ

pF

8. Applies to noncascaded/nonsynchronous clocked configurations only with synchronously cascaded counters. (1) Clock to Ripple Carry Out

propagation delays. (2) Enable T or Enable P to Clock setup times and (3) Clock to Enable T or Enable P hold times determine f

max

. However,

if Ripple Carry out of each stage is tied to the Clock of the next stage (nonsynchronously clocked) the f

max

in the table above is applicable.

See Applications information in this data sheet.

9. For propagation delays with loads other than 50 pF, and information on typical parametric values, see the ON Semiconductor High−Speed

CMOS Data Book (DL129/D).

C

PD

Power Dissipation Capacitance (Per Gate) (Note 10)

Typical @ 25°C, V

CC

= 5.0 V

pF

45

10.Used to determine the no−load dynamic power consumption: P

D

= C

PD

V

CC

2

f + I

CC

V

CC

. For load considerations, see the ON

Semiconductor High−Speed CMOS Data Book (DL129/D).

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件