Datasheet 搜索 > 微控制器 > Freescale(飞思卡尔) > MC9S12C128CFAE 数据手册 > MC9S12C128CFAE 数据手册 45/690 页

器件3D模型

器件3D模型¥ 73.276

MC9S12C128CFAE 数据手册 - Freescale(飞思卡尔)

制造商:

Freescale(飞思卡尔)

分类:

微控制器

封装:

LQFP-48

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P45P46P47P76P77P107P132P133P195P679Hot

典型应用电路图在P267P666

原理图在P20P74P109P130P157P165P193P194P195P224P252P253

封装尺寸在P681P682P683P684

型号编码规则在P686P687P688

封装信息在P653

功能描述在P76P77P104P150P161P167P174P212P245P266P289P323

技术参数、封装参数在P649

电气规格在P647P648P649P650P651P652P653P654P655P656P657P658

导航目录

MC9S12C128CFAE数据手册

Page:

of 690 Go

若手册格式错乱,请下载阅览PDF原文件

Chapter 1 MC9S12C and MC9S12GC Device Overview (MC9S12C128)

Freescale Semiconductor MC9S12C-Family / MC9S12GC-Family 45

Rev 01.24

1.3 Signal Description

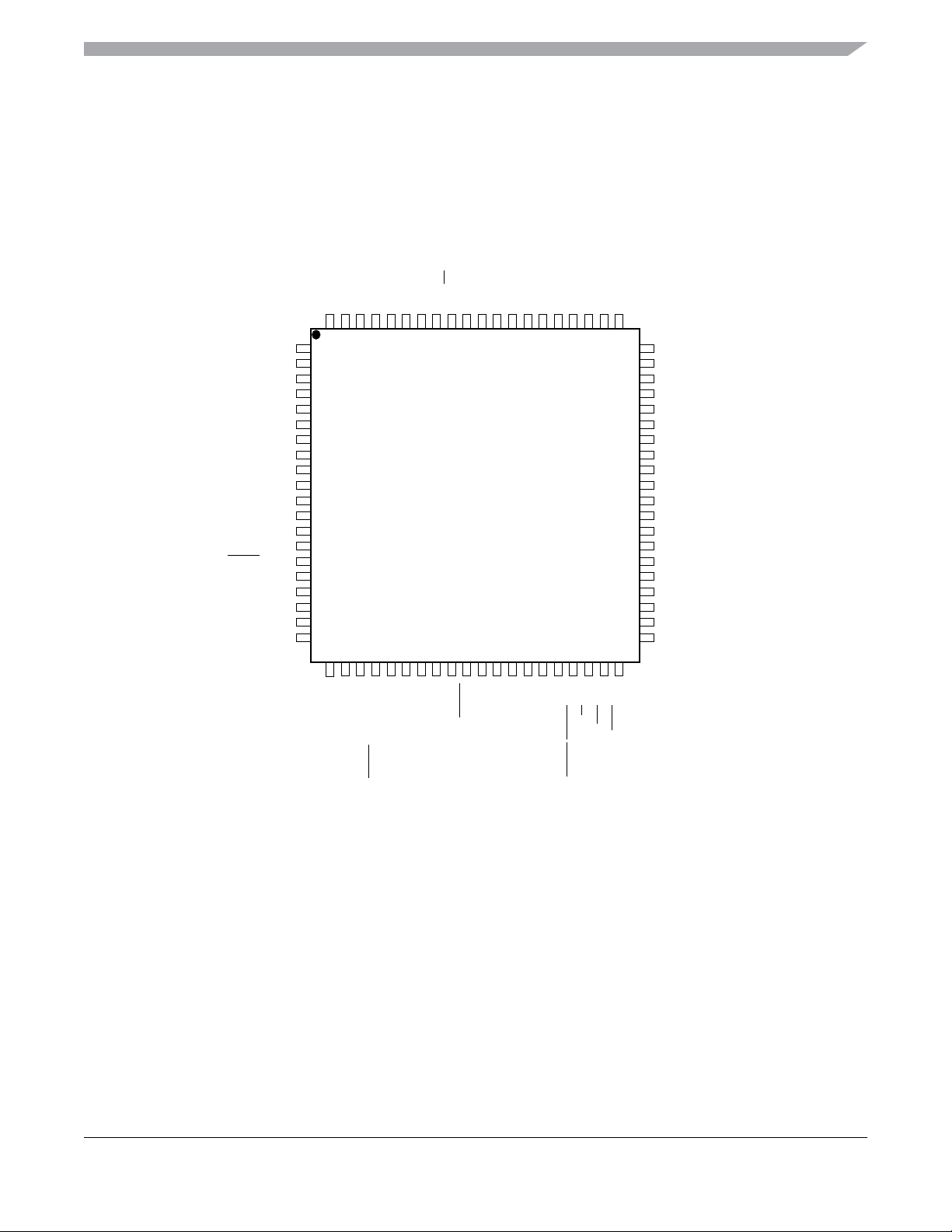

1.3.1 Device Pinouts

Figure 1-7. Pin Assignments in 80-Pin QFP

The MODRR register within the PIM allows for mapping of PWM channels to Port T in the absence of

Port P pins for the low pin count packages. For the 80QFP package option it is recommended not to use

MODRR since this is intended to support PWM channel availability in low pin count packages. Note that

when mapping PWM channels to Port T in an 80QFP option, the associated PWM channels are then

mapped to both Port P and Port T

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

MC9S12C-Family /

MC9S12GC-Family

V

RH

V

DDA

PAD07/AN07

PAD06/AN06

PAD05/AN05

PAD04/AN04

PAD03/AN03

PAD02/AN02

PAD01/AN01

PAD00/AN00

V

SS2

V

DD2

PA7/ADDR15/DATA1

5

PA6/ADDR14/DATA1

4

PA5/ADDR13/DATA1

3

PA4/ADDR12/DATA1

2

PA3/ADDR11/DATA11

PA2/ADDR10/DATA1

0

PA1/ADDR9/DATA9

PA0/ADDR8/DATA8

PP4/KWP4/PW4

PP5/KWP5/PW5

PP7/KWP7

V

DDX

V

SSX

PM0/RXCAN

PM1/TXCAN

PM2/MISO

PM3/

SS

PM4/MOSI

PM5/SCK

PJ6/KWJ6

PJ7/KWJ7

PP6/KWP6/ROMCT

L

PS3

PS2

PS1/TXD

PS0/RXD

V

SSA

V

RL

PW3/KWP3/PP3

PW2/KWP2/PP2

PW1/KWP1/PP1

PW0/KWP0/PP0

PW0/IOC0/PT0

PW1/IOC1/PT1

PW2/IOC2/PT2

PW3/IOC3/PT3

V

DD1

V

SS1

PW4/IOC4/PT4

IOC5/PT5

IOC6/PT6

IOC7/PT7

MODC/TAGHI/BKGD

ADDR0/DATA0/PB0

ADDR1/DATA1/PB1

ADDR2/DATA2/PB2

ADDR3/DATA3/PB3

ADDR4/DATA4/PB4

ADDR5/DATA5/PB5

ADDR6/DATA6/PB6

ADDR7/DATA7/PB7

XCLKS/NOACC/PE7

MODB/IPIPE1/PE6

MODA/IPIPE0/PE5

ECLK/PE4

V

SSR

V

DDR

RESET

V

DDPLL

XFC

V

SSPLL

EXTAL

XTAL

V

PP

/TEST

LSTRB/TAGLO/PE3

R/

W/PE2

IRQ/PE1

XIRQ/PE0

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

Signals shown in Bold are not available on the 52- or 48-pin package

Signals shown in Bold Italic are available in the 52-pin, but not the 48-pin package

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件