Datasheet 搜索 > 微控制器 > Freescale(飞思卡尔) > MC9S12XDP512CAG 数据手册 > MC9S12XDP512CAG 数据手册 352/1348 页

器件3D模型

器件3D模型¥ 348.974

MC9S12XDP512CAG 数据手册 - Freescale(飞思卡尔)

制造商:

Freescale(飞思卡尔)

分类:

微控制器

封装:

LQFP-144

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P49P50P51P694P746P808P809P810P811P812P813P814Hot

典型应用电路图在P98P1268

原理图在P34P35P36P81P120P125P126P160P161P185P310P351

封装尺寸在P1288P1289P1290P1291

型号编码规则在P1306

封装信息在P1243

功能描述在P98P122P152P180P202P350P380P409P421P456P493P528

技术参数、封装参数在P1239

电气规格在P122P799P1237P1238P1239P1240P1241P1242P1243P1244P1245P1246

型号编号列表在P1306

导航目录

MC9S12XDP512CAG数据手册

Page:

of 1348 Go

若手册格式错乱,请下载阅览PDF原文件

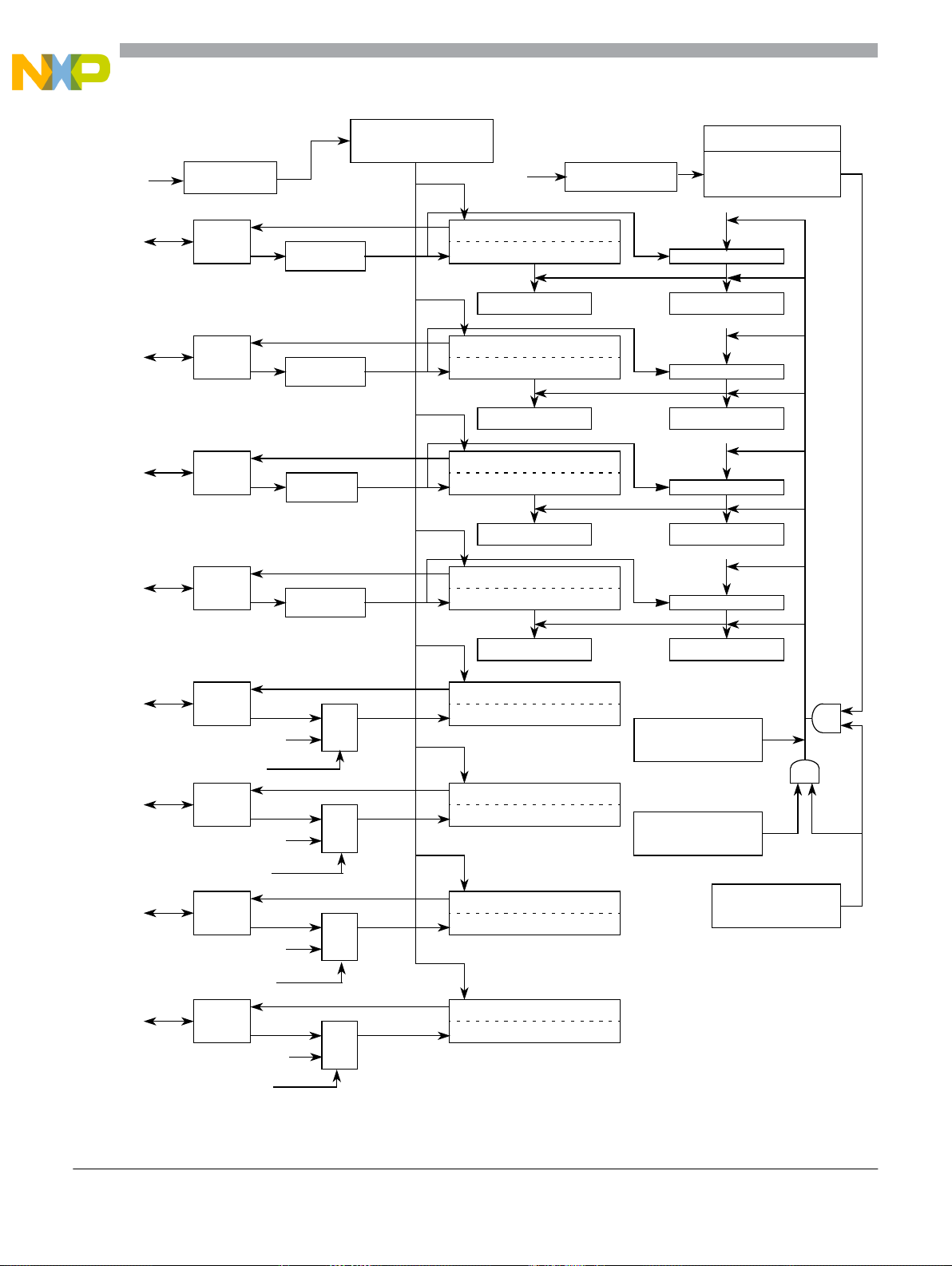

Chapter 7 Enhanced Capture Timer (S12ECT16B8CV2)

MC9S12XDP512 Data Sheet, Rev. 2.21

352 Freescale Semiconductor

Figure 7-66. Detailed Timer Block Diagram in Latch Mode when PRNT = 1

16 BIT MAIN TIMER

P1

Comparator

TC0H Hold Reg.

P0

P3

P2

P4

P5

P6

P7

EDG0

EDG1

EDG2

EDG3

MUX

Modulus Prescaler

Bus Clock

16-Bit Load Register

16-Bit Modulus

0

RESET

EDG0

EDG1

EDG2

EDG4

EDG5

EDG3

EDG6

EDG7

÷ 1, 2,3, ..., 256

16-Bit Free-Running

LATCH

Underflow

Main Timer

Timer Prescaler

TC0 Capture/Compare Reg.

Comparator

TC1 Capture/Compare Reg.

Comparator

TC2 Capture/Compare Reg.

Comparator

TC3 Capture/Compare Reg.

Comparator

TC4 Capture/Compare Reg.

Comparator

TC5 Capture/Compare Reg.

Comparator

TC6 Capture/Compare Reg.

Comparator

TC7 Capture/Compare Reg.

Pin Logic

Pin Logic

Pin Logic

Pin Logic

Pin Logic

Pin Logic

Pin Logic

Pin Logic

Delay

TC1H Hold Reg.

TC2H Hold Reg.

TC3H Hold Reg.

MUX

MUX

MUX

PA0H Hold Reg.

PAC0

0

RESET

PA1H Hold Reg.

PAC1

0

RESET

PA2H Hold Reg.

PAC2

0

RESET

PA3H Hold Reg.

PAC3

Write 0x0000

to Modulus Counter

ICLAT, LATQ, BUFEN

(Force Latch)

LATQ

(MDC Latch Enable)

Down Counter

SH04

SH15

SH26

SH37

Bus Clock

÷ 1, 2,3, ..., 256

Counter

Delay

Counter

Delay

Counter

Delay

Counter

8, 12, 16, ..., 1024

8, 12, 16, ..., 1024

8, 12, 16, ..., 1024

8, 12, 16, ..., 1024

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件