Datasheet 搜索 > 微控制器 > Freescale(飞思卡尔) > MC9S12XDP512CAL 数据手册 > MC9S12XDP512CAL 数据手册 886/1348 页

器件3D模型

器件3D模型¥ 148.14

MC9S12XDP512CAL 数据手册 - Freescale(飞思卡尔)

制造商:

Freescale(飞思卡尔)

分类:

微控制器

封装:

LQFP-112

描述:

16位微控制器 - MCU 9S12XDP512 TSMC3 GENERAL

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P49P50P51P694P746P808P809P810P811P812P813P814Hot

典型应用电路图在P98P1268

原理图在P34P35P36P81P120P125P126P160P161P185P310P351

封装尺寸在P1288P1289P1290P1291

型号编码规则在P1306

封装信息在P1243

功能描述在P98P122P152P180P202P350P380P409P421P456P493P528

技术参数、封装参数在P1239

电气规格在P122P799P1237P1238P1239P1240P1241P1242P1243P1244P1245P1246

型号编号列表在P1306

导航目录

MC9S12XDP512CAL数据手册

Page:

of 1348 Go

若手册格式错乱,请下载阅览PDF原文件

Chapter 22 DP512 Port Integration Module (S12XDP512PIMV2)

MC9S12XDP512 Data Sheet, Rev. 2.21

888 Freescale Semiconductor

A valid edge on an input is detected if 4 consecutive samples of a passive level are followed by

4 consecutive samples of an active level directly or indirectly.

The filters are continuously clocked by the bus clock in run and wait mode. In stop mode, the clock is

generated by an RC-oscillator in the port integration module. To maximize current saving the RC

oscillator runs only if the following condition is true on any pin individually:

Sample count <= 4 and interrupt enabled (PIE = 1) and interrupt flag not set (PIF = 0).

22.4.4 Expanded Bus Pin Functions

All peripheral ports T, S, M, P, H, J, AD0, and AD1 start up as general purpose inputs after reset.

Depending on the external mode pin condition, the external bus interface related ports A, B, C, D, E, and

K start up as general purpose inputs on reset or are configured for their alternate functions.

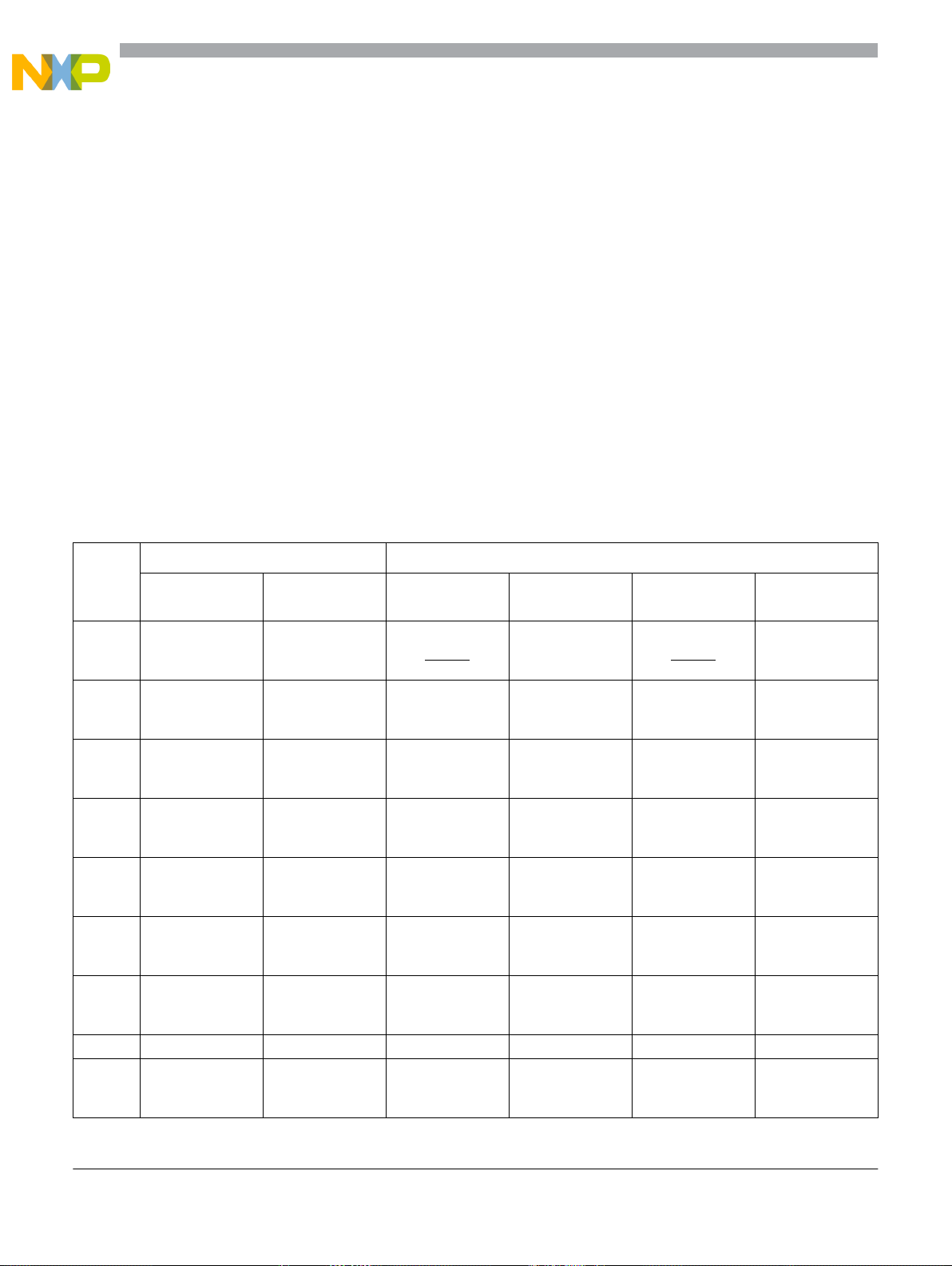

Table 22-70 lists the pin functions in relationship with the different operating modes. If two entries per pin

are displayed, a ‘mux’ indicates time-multiplexing between the two functions and an ‘or’ means that a

configuration bit exists which can be altered after reset to select the respective function (displayed in

italics). Refer to S12X_EBI section for details.

Table 22-70. Expanded Bus Pin Functions versus Operating Modes

Pin

Single-Chip Modes Expanded Modes

Normal

Single-Chip

Special

Single-Chip

Normal

Expanded

Emulation

Single-Chip

Emulation

Expanded

Special

Test

PK7 GPIO GPIO GPIO

or

EWAIT

GPIO GPIO

or

EWAIT

GPIO

PK[6:4] GPIO GPIO ADDR[22:20]

or

GPIO

ADDR[22:20]

mux

ACC[2:0]

ADDR[22:20]

mux

ACC[2:0]

ADDR[22:20]

PK[3:0] GPIO GPIO ADDR[19:16]

or

GPIO

ADDR[19:16]

mux

IQSTAT[3:0]

ADDR[19:16]

mux

IQSTAT[3:0]

ADDR[19:16]

PA[7:0] GPIO GPIO ADDR[15:8]

or

GPIO

ADDR[15:8]

mux

IVD[15:8]

ADDR[15:8]

mux

IVD[15:8]

ADDR[15:8]

PB[7:1] GPIO GPIO ADDR[7:1]

or

GPIO

ADDR[7:1]

mux

IVD[7:1]

ADDR[7:1]

mux

IVD[7:1]

ADDR[7:1]

PB0 GPIO GPIO UDS

or

GPIO

ADDR0

mux

IVD0

ADDR0

mux

IVD0

ADDR0

PC[7:0] GPIO GPIO DATA[15:8]

or

GPIO

DATA[15:8] DATA[15:8] DATA[15:8]

or

GPIO

PD[7:0] GPIO GPIO DATA[7:0] DATA[7:0] DATA[7:0] DATA[7:0]

PE7 GPIO

or

ECLKX2

GPIO

or

ECLKX2

GPIO

or

ECLKX2

ECLKX2 ECLKX2 GPIO

or

ECLKX2

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件