Datasheet 搜索 > 数字电位器 > Microchip(微芯) > MCP42050T-E/ST 数据手册 > MCP42050T-E/ST 数据手册 5/32 页

器件3D模型

器件3D模型¥ 5.195

MCP42050T-E/ST 数据手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

数字电位器

封装:

TSSOP-14

描述:

数字电位计 IC 256 Step SPI 50kOhm

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

MCP42050T-E/ST数据手册

Page:

of 32 Go

若手册格式错乱,请下载阅览PDF原文件

2003 Microchip Technology Inc. DS11195C-page 5

MCP41XXX/42XXX

Absolute Maximum Ratings †

V

DD

...................................................................................7.0V

All inputs and outputs w.r.t. V

SS

............... -0.6V to V

DD

+1.0V

Storage temperature .....................................-60°C to +150°C

Ambient temp. with power applied ................-60°C to +125°C

ESD protection on all pins ..................................................≥ 2kV

† Notice:

Stresses above those listed under “maximum rat-

ings” may cause permanent damage to the device. This is a

stress rating only and functional operation of the device at

those or any other conditions above those indicated in the

operational listings of this specification is not implied. Expo-

sure to maximum rating conditions for extended periods may

affect device reliability.

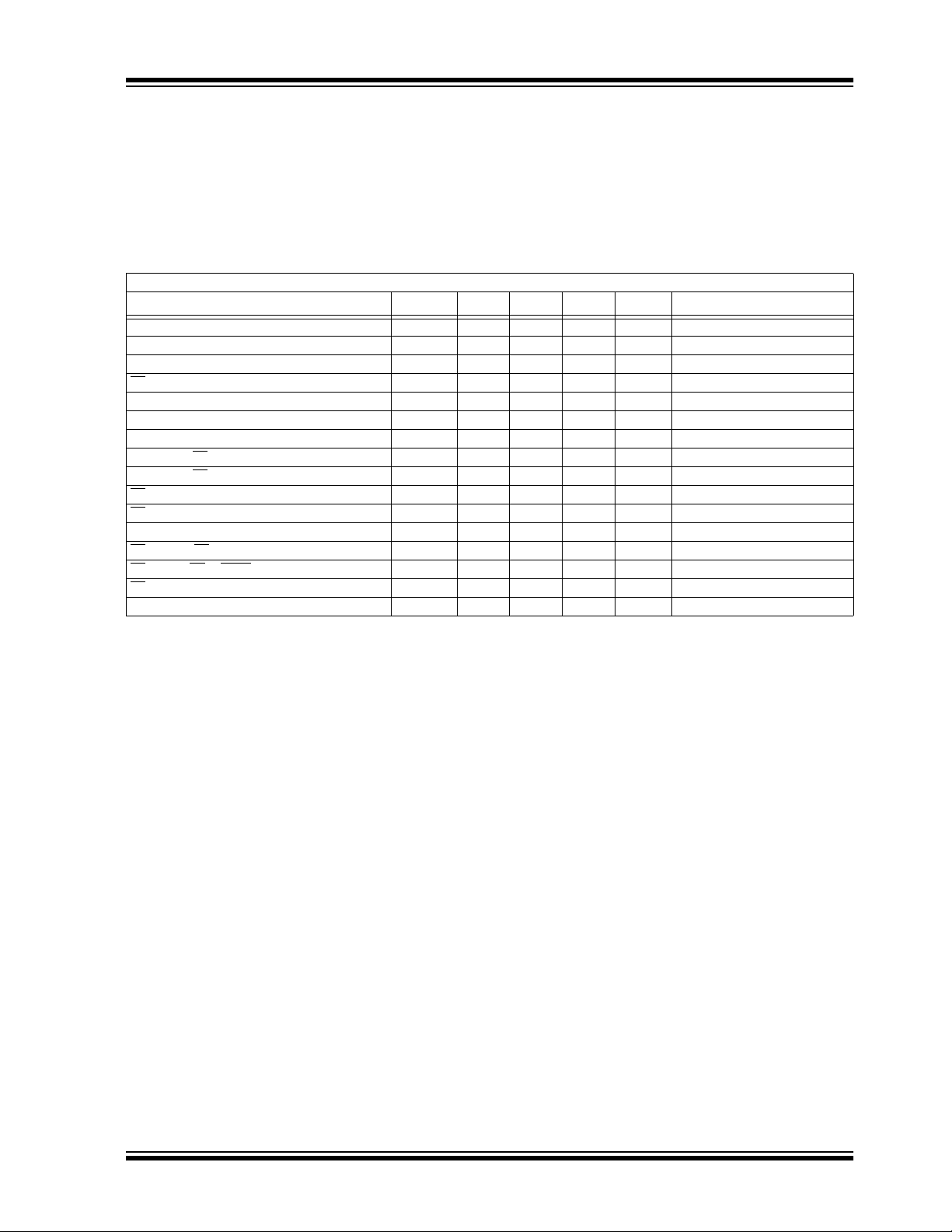

AC TIMING CHARACTERISTICS

Electrical Characteristics: Unless otherwise indicated, V

DD

= +2.7V to 5.5V, T

A

= -40°C to +85°C.

Parameter Sym Min. Typ. Max. Units Conditions

Clock Frequency F

CLK

——10MHzV

DD

= 5V (Note 1)

Clock High Time t

HI

40 — — ns

Clock Low Time t

LO

40 — — ns

CS

Fall to First Rising CLK Edge t

CSSR

40 — — ns

Data Input Setup Time t

SU

40 — — ns

Data Input Hold Time t

HD

10 — — ns

SCK Fall to SO Valid Propagation Delay t

DO

—80 nsC

L

= 30 pF (Note 2)

SCK Rise to CS

Rise Hold Time t

CHS

30 — — ns

SCK Rise to CS

Fall Delay t

CS0

10 — — ns

CS

Rise to CLK Rise Hold t

CS1

100 — — ns

CS

High Time t

CSH

40 — — ns

Reset Pulse Width t

RS

150 — — ns Note 2

RS

Rising to CS Falling Delay Time t

RSCS

150 — — ns Note 2

CS

rising to RS or SHDN falling delay time t

SE

40 — — ns Note 3

CS

low time t

CSL

100 — — ns Note 3

Shutdown Pulse Width t

SH

150 — — ns Note 3

Note 1: When using the device in the daisy-chain configuration, maximum clock frequency is determined by a combination of propagation delay

time (t

DO

) and data input setup time (t

SU

). Max. clock frequency is therefore ~ 5.8 MHz based on SCK rise and fall times of 5 ns, t

HI

=

40 ns, t

DO

= 80 ns and t

SU

= 40 ns.

2: Applies only to the MCP42XXX devices.

3: Applies only when using hardware pins to exit software shutdown mode, MCP42XXX only.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件