Datasheet 搜索 > NXP(恩智浦) > MRF1518N 数据手册 > MRF1518N 数据手册 1/7 页

¥ 0

MRF1518N 数据手册 - NXP(恩智浦)

制造商:

NXP(恩智浦)

封装:

PLD-3

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

原理图在P3P5

导航目录

MRF1518N数据手册

Page:

of 7 Go

若手册格式错乱,请下载阅览PDF原文件

Using Data Sheet Impedances

for RF LDMOS Devices

By: Darin Wagner

INTRODUCTION

This document explains the format used by Freescale for

presenting LDMOS impedance information for both

single -ended and push -pull devices on RF Power data

sheets. The purpose of this document is to clarify the use of

this information in the initial design of input and output

matching networks for these devices.

Multiple methods are available for impedance extraction.

The scope of this document does not cover detailed extraction

methods; however, a possible extraction method is explained

here. Whichever method is used, the main concern to be

addressed is the need to de-embed the extracted data back

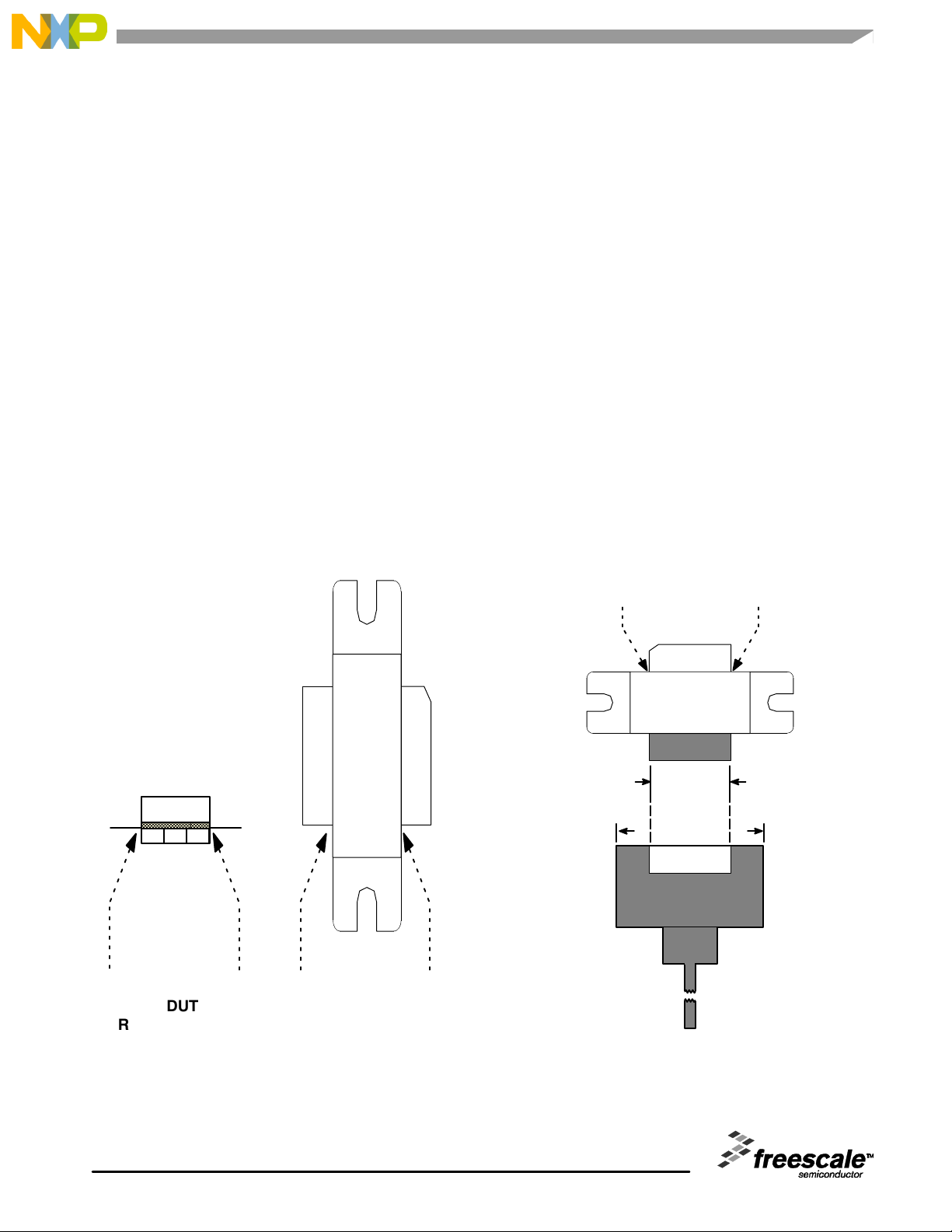

to the reference plane of the device as shown in Figure 1.

As a byproduct of the impedance extraction methodology,

a zero length width step simulation block should be used

during simulation The MSTEP block for Agilent Advanced

Design System (ADS) users shows the difference between

the reference plane width and the copper lead pad width.

Figure 2 illustrates that the copper lead pad width (Dimension

“b”) is larger than the reference plane width (Dimension “a”).

For more information on this topic, the reference provided

at the end of this document is a rigorous but accurate method

for impedance measurements:

ÎÎÎÎ

DUT

Reference Planes

DUT

Reference Planes

b

a

MRF

XXXXX

DUT Reference Plane

Figure 1. Location of Reference Planes on a Package

Figure 2. Illustration of the Instantaneous

Impedance Change and Need for MSTEP Blocks

b

EB212

Rev. 0, 1/2004

Freescale Semiconductor

Engineering Bulletin

Freescale Semiconductor, Inc., 2004, 2006. All rights reserved.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件