Datasheet 搜索 > 微控制器 > Microchip(微芯) > PIC18F45K20T-I/PT 数据手册 > PIC18F45K20T-I/PT 数据手册 138/440 页

器件3D模型

器件3D模型¥ 7.442

PIC18F45K20T-I/PT 数据手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

TQFP-44

描述:

PIC18 系列 1536 B RAM 32 kB 闪存 8位 微控制器 - TQFP-44

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P3P116P135P136P138P163Hot

典型应用电路图在P184

原理图在P12P14P15P26P34P39P48P131P137P138P140P146

封装尺寸在P413

标记信息在P410P411P412

封装信息在P410P414P415P416P418P422P423P426P427P428P432P433

技术参数、封装参数在P11P12P36P93P260P264P266P269P272P273P361P362

应用领域在P30P166P173P280

电气规格在P11P12P36P93P260P264P266P269P272P273

导航目录

PIC18F45K20T-I/PT数据手册

Page:

of 440 Go

若手册格式错乱,请下载阅览PDF原文件

PIC18F2XK20/4XK20

DS40001303H-page 138 2010-2015 Microchip Technology Inc.

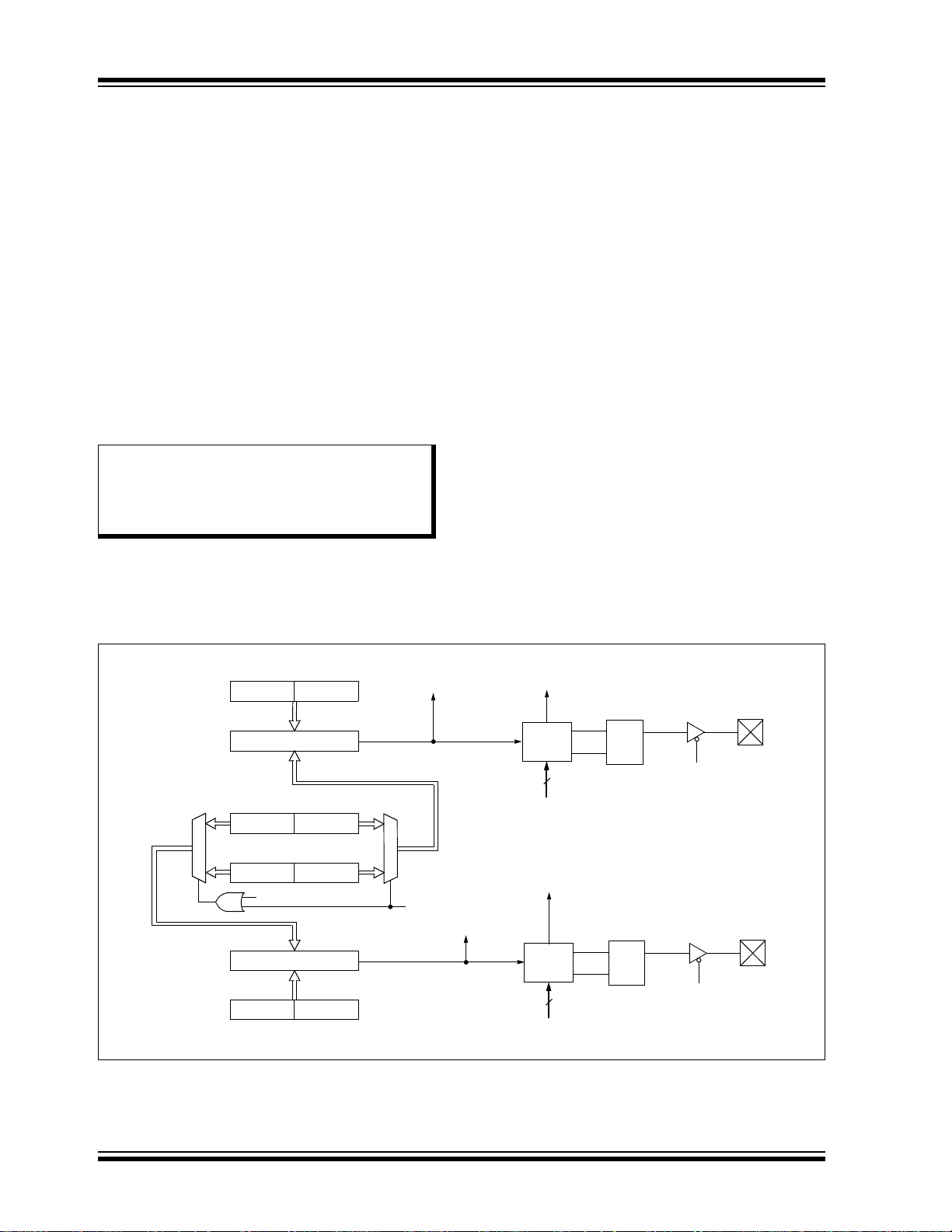

11.3 Compare Mode

In Compare mode, the 16-bit CCPRx register value is

constantly compared against either the TMR1 or TMR3

register pair value. When a match occurs, the CCPx pin

can be:

• driven high

• driven low

• toggled (high-to-low or low-to-high)

• remain unchanged (that is, reflects the state of the

I/O latch)

The action on the pin is based on the value of the mode

select bits (CCPxM<3:0>). At the same time, the inter-

rupt flag bit, CCPxIF, is set.

11.3.1 CCP PIN CONFIGURATION

The user must configure the CCPx pin as an output by

clearing the appropriate TRIS bit.

11.3.2 TIMER1/TIMER3 MODE SELECTION

Timer1 and/or Timer3 must be running in Timer mode

or Synchronized Counter mode if the CCP module is

using the compare feature. In Asynchronous Counter

mode, the compare operation will not work reliably.

11.3.3 SOFTWARE INTERRUPT MODE

When the Generate Software Interrupt mode is chosen

(CCPxM<3:0> = 1010), the corresponding CCPx pin is

not affected. Only the CCPxIF interrupt flag is affected.

11.3.4 SPECIAL EVENT TRIGGER

Both CCP modules are equipped with a Special Event

Trigger. This is an internal hardware signal generated

in Compare mode to trigger actions by other modules.

The Special Event Trigger is enabled by selecting

the Compare Special Event Trigger mode

(CCPxM<3:0> = 1011).

For either CCP module, the Special Event Trigger resets

the timer register pair for whichever timer resource is

currently assigned as the module’s time base. This

allows the CCPRx registers to serve as a programmable

period register for either timer.

The Special Event Trigger for CCP2 can also start an

A/D conversion. In order to do this, the A/D converter

must already be enabled.

FIGURE 11-2: COMPARE MODE OPERATION BLOCK DIAGRAM

Note: Clearing the CCPxCON register will force

the CCPx compare output latch (depend-

ing on device configuration) to the default

low level. This is not the PORTB or

PORTC I/O data latch.

CCPR1H CCPR1L

TMR1H TMR1L

Comparator

Q

S

R

Output

Logic

Special Event Trigger

Set CCP1IF

CCP1 pin

TRIS

CCP1CON<3:0>

Output Enable

TMR3H TMR3L

CCPR2H CCPR2L

Comparator

1

0

T3CCP2

T3CCP1

Set CCP2IF

1

0

Compare

4

(Timer1/Timer3 Reset)

Q

S

R

Output

Logic

Special Event Trigger

CCP2 pin

TRIS

CCP2CON<3:0>

Output Enable

4

(Timer1/Timer3 Reset, A/D Trigger)

Match

Compare

Match

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件