Datasheet 搜索 > 微控制器 > Microchip(微芯) > PIC24FV32KA304T-I/MV 数据手册 > PIC24FV32KA304T-I/MV 数据手册 233/364 页

器件3D模型

器件3D模型¥ 35.184

PIC24FV32KA304T-I/MV 数据手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

UQFN-48

描述:

PIC 32MHz 闪存:11K@x24bit RAM:2KB

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P3P4P5P6P7P16P17P18P19P20P21P22Hot

典型应用电路图在P232P233

原理图在P15P30P69P135P139P142P143P147P152P154P161P162

封装尺寸在P328

标记信息在P325

封装信息在P265P325P331P333P334P335P336P337P338P339P347P348

功能描述在P11P65P147P151P185

技术参数、封装参数在P265P272P273P274P275P276P278P280P293

应用领域在P127

电气规格在P25P72P74P206P219P243P248P352

导航目录

PIC24FV32KA304T-I/MV数据手册

Page:

of 364 Go

若手册格式错乱,请下载阅览PDF原文件

2011-2013 Microchip Technology Inc. DS39995D-page 233

PIC24FV32KA304 FAMILY

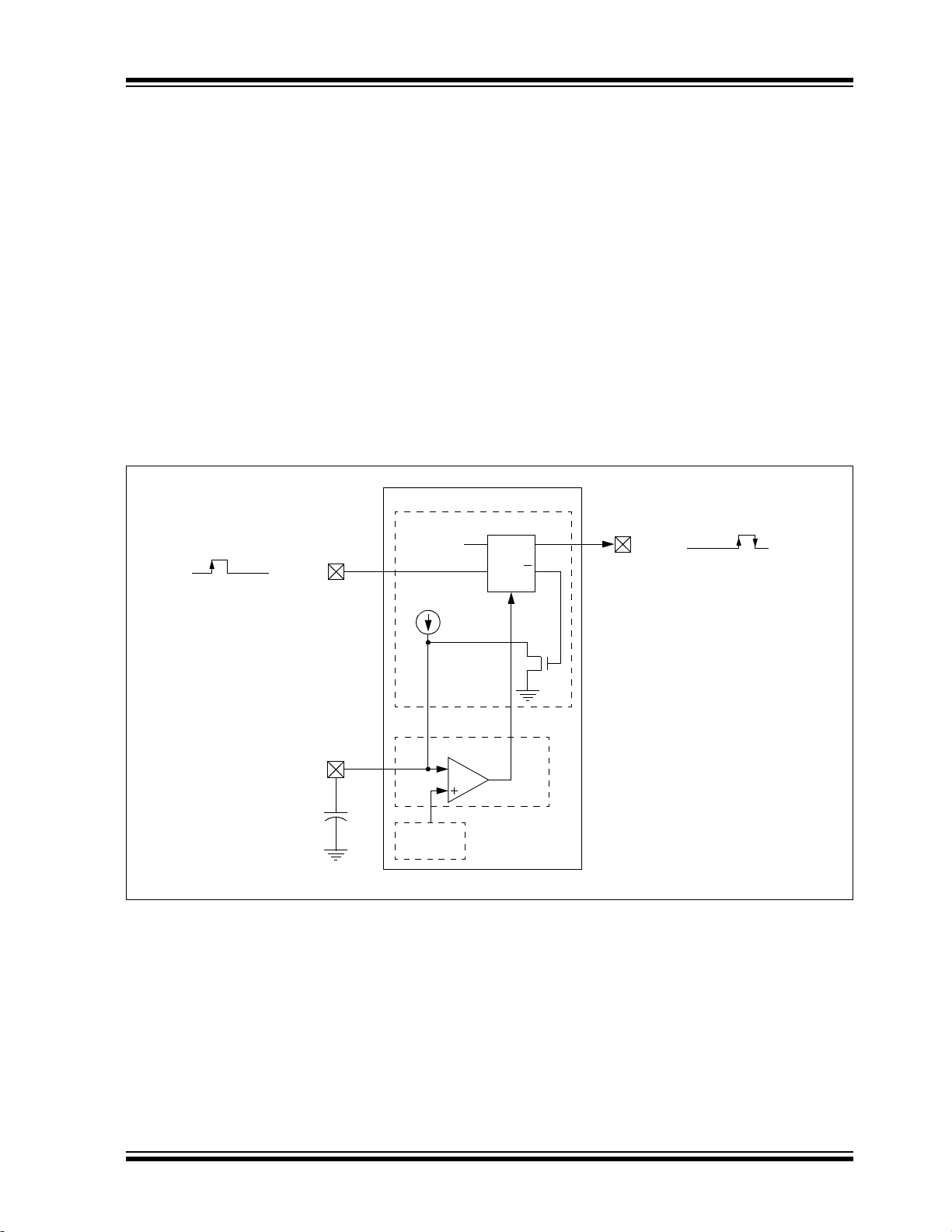

25.3 Pulse Generation and Delay

The CTMU module can also generate an output pulse

with edges that are not synchronous with the device’s

system clock. More specifically, it can generate a pulse

with a programmable delay from an edge event input to

the module.

When the module is configured for pulse generation

delay by setting the TGEN bit (CTMUCON<12>), the

internal current source is connected to the B input of

Comparator 2. A capacitor (C

DELAY) is connected to

the Comparator 2 pin, C2INB, and the Comparator

Voltage Reference, CVREF, is connected to C2INA.

CV

REF is then configured for a specific trip point. The

module begins to charge C

DELAY when an edge event

is detected. While CV

REF is greater than the voltage on

C

DELAY, CTPLS is high.

When the voltage on C

DELAY equals CVREF, CTPLS

goes low. With Comparator 2 configured as the second

edge, this stops the CTMU from charging. In this state

event, the CTMU automatically connects to ground.

The IDISSEN bit doesn’t need to be set and cleared

before the next CTPLS cycle.

Figure 25-3 illustrates the external connections for

pulse generation, as well as the relationship of the

different analog modules required. While CTED1 is

shown as the input pulse source, other options are

available. A detailed discussion on pulse generation

with the CTMU module is provided in the “PIC24F

Family Reference Manual”.

FIGURE 25-3: TYPICAL CONNECTIONS AND INTERNAL CONFIGURATION FOR PULSE

DELAY GENERATION

C2

CVREF

CTPLS

PIC24F Device

Current

Comparator

CTMU

CTED1

C2INB

CDELAY

EDG1

–

EDG2

Source

VDD

EDG1 EDG2

Q

Q

D

CK

R

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件