Datasheet 搜索 > 微控制器 > Microchip(微芯) > PIC32MX460F512L-80I/PT 数据手册 > PIC32MX460F512L-80I/PT 数据手册 103/214 页

器件3D模型

器件3D模型¥ 59.502

PIC32MX460F512L-80I/PT 数据手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

TQFP-100

描述:

MICROCHIP PIC32MX460F512L-80I/PT 微控制器, 32位, 常规性能, PIC32, 80 MHz, 512 KB, 32 KB, 100 引脚, TQFP

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P6P7P8P9P12P13P14P15P22P23P24P25Hot

原理图在P21P37P87P95P97P101P103P105P106P107P109P111

封装尺寸在P192P204

标记信息在P191P204

封装信息在P4P5P152P191P193P194P195P196P198P199P200P201

功能描述在P43P119

技术参数、封装参数在P152P157P158P160P161P163P179P180P188P206P208

电气规格在P32P102P138P158P188P204P206P208

导航目录

PIC32MX460F512L-80I/PT数据手册

Page:

of 214 Go

若手册格式错乱,请下载阅览PDF原文件

© 2011 Microchip Technology Inc. DS61143H-page 103

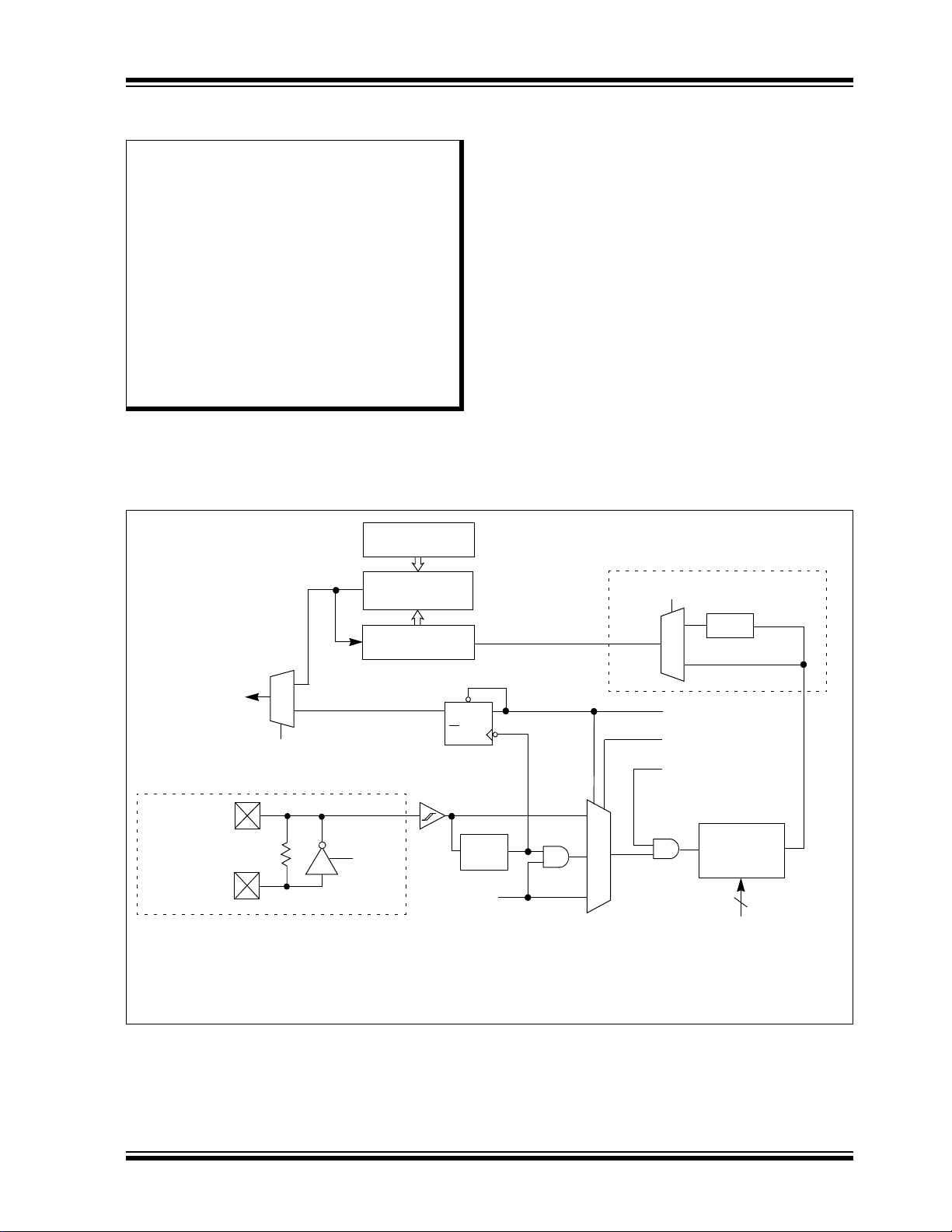

PIC32MX3XX/4XX

13.0 TIMER1

This family of PIC32MX devices features one

synchronous/asynchronous 16-bit timer that can oper-

ate as a free-running interval timer for various timing

applications and counting external events. This timer

can also be used with the Secondary Oscillator (S

OSC)

for real-time clock applications. The following modes

are supported:

• Synchronous Internal Timer

• Synchronous Internal Gated Timer

• Synchronous External Timer

• Asynchronous External Timer

13.1 Additional Supported Features

• Selectable clock prescaler

• Timer operation during CPU Idle and Sleep mode

• Fast bit manipulation using CLR, SET and INV

registers

• Asynchronous mode can be used with the S

OSC

to function as a Real-Time Clock (RTC)

FIGURE 13-1: TIMER1 BLOCK DIAGRAM

(1)

Note 1: This data sheet summarizes the features

of the PIC32MX3XX/4XX family of

devices. It is not intended to be a compre-

hensive reference source. To comple-

ment the information in this data sheet,

refer to Section 14. “Timers” (DS61105)

of the “PIC32 Family Reference Manual”,

which is available from the Microchip web

site (www.microchip.com/PIC32).

2: Some registers and associated bits

described in this section may not be

available on all devices. Refer to

Section 4.0 “Memory Organization” in

this data sheet for device-specific register

and bit information.

ON (T1CON<15>)

Sync

SOSCI

SOSCO/T1CK

PR1

T1IF

Equal

16-bit Comparator

TMR1

Reset

SOSCEN

Event Flag

1

0

TSYNC (T1CON<2>)

TGATE (T1CON<7>)

TGATE (T1CON<7>)

PBCLK

1

0

TCS (T1CON<1>)

Gate

Sync

TCKPS<1:0>

Prescaler

2

1, 8, 64, 256

x 1

1 0

0 0

Q

QD

(T1CON<5:4>)

Note 1: The default state of the SOSCEN (OSCCON<1>) during a device Reset is controlled by the FSOSCEN bit in

Configuration Word DEVCFG1.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件