Datasheet 搜索 > 微控制器 > Microchip(微芯) > PIC32MX460F512L-80I/PT 数据手册 > PIC32MX460F512L-80I/PT 数据手册 37/214 页

器件3D模型

器件3D模型¥ 59.502

PIC32MX460F512L-80I/PT 数据手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

TQFP-100

描述:

MICROCHIP PIC32MX460F512L-80I/PT 微控制器, 32位, 常规性能, PIC32, 80 MHz, 512 KB, 32 KB, 100 引脚, TQFP

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P6P7P8P9P12P13P14P15P22P23P24P25Hot

原理图在P21P37P87P95P97P101P103P105P106P107P109P111

封装尺寸在P192P204

标记信息在P191P204

封装信息在P4P5P152P191P193P194P195P196P198P199P200P201

功能描述在P43P119

技术参数、封装参数在P152P157P158P160P161P163P179P180P188P206P208

电气规格在P32P102P138P158P188P204P206P208

导航目录

PIC32MX460F512L-80I/PT数据手册

Page:

of 214 Go

若手册格式错乱,请下载阅览PDF原文件

© 2011 Microchip Technology Inc. DS61143H-page 37

PIC32MX3XX/4XX

3.0 CPU

The MIPS32

®

M4K

®

Processor Core is the heart of the

PIC32MX3XX/4XX family processor. The CPU fetches

instructions, decodes each instruction, fetches source

operands, executes each instruction and writes the

results of instruction execution to the proper destina-

tions.

3.1 Features

• 5-stage pipeline

• 32-bit Address and Data Paths

• MIPS32 Enhanced Architecture (Release 2)

- Multiply-Accumulate and Multiply-Subtract

Instructions

- Targeted Multiply Instruction

- Zero/One Detect Instructions

- WAIT Instruction

- Conditional Move Instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers to minimize latency

for interrupt handlers

- Bit field manipulation instructions

• MIPS16e

®

Code Compression

- 16-bit encoding of 32-bit instructions to

improve code density

- Special PC-relative instructions for efficient

loading of addresses and constants

- SAVE & RESTORE macro instructions for

setting up and tearing down stack frames

within subroutines

- Improved support for handling 8 and 16-bit

data types

• Simple Fixed Mapping Translation (FMT)

mechanism

• Simple Dual Bus Interface

- Independent 32-bit address and data busses

- Transactions can be aborted to improve

interrupt latency

• Autonomous Multiply/Divide Unit

- Maximum issue rate of one 32x16 multiply

per clock

- Maximum issue rate of one 32x32 multiply

every other clock

- Early-in iterative divide. Minimum 11 and

maximum 34 clock latency (dividend (rs) sign

extension-dependent)

• Power Control

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT

instruction)

- Extensive use of local gated clocks

• EJTAG Debug and Instruction Trace

- Support for single stepping

- Virtual instruction and data address/value

- breakpoints

- PC tracing with trace compression

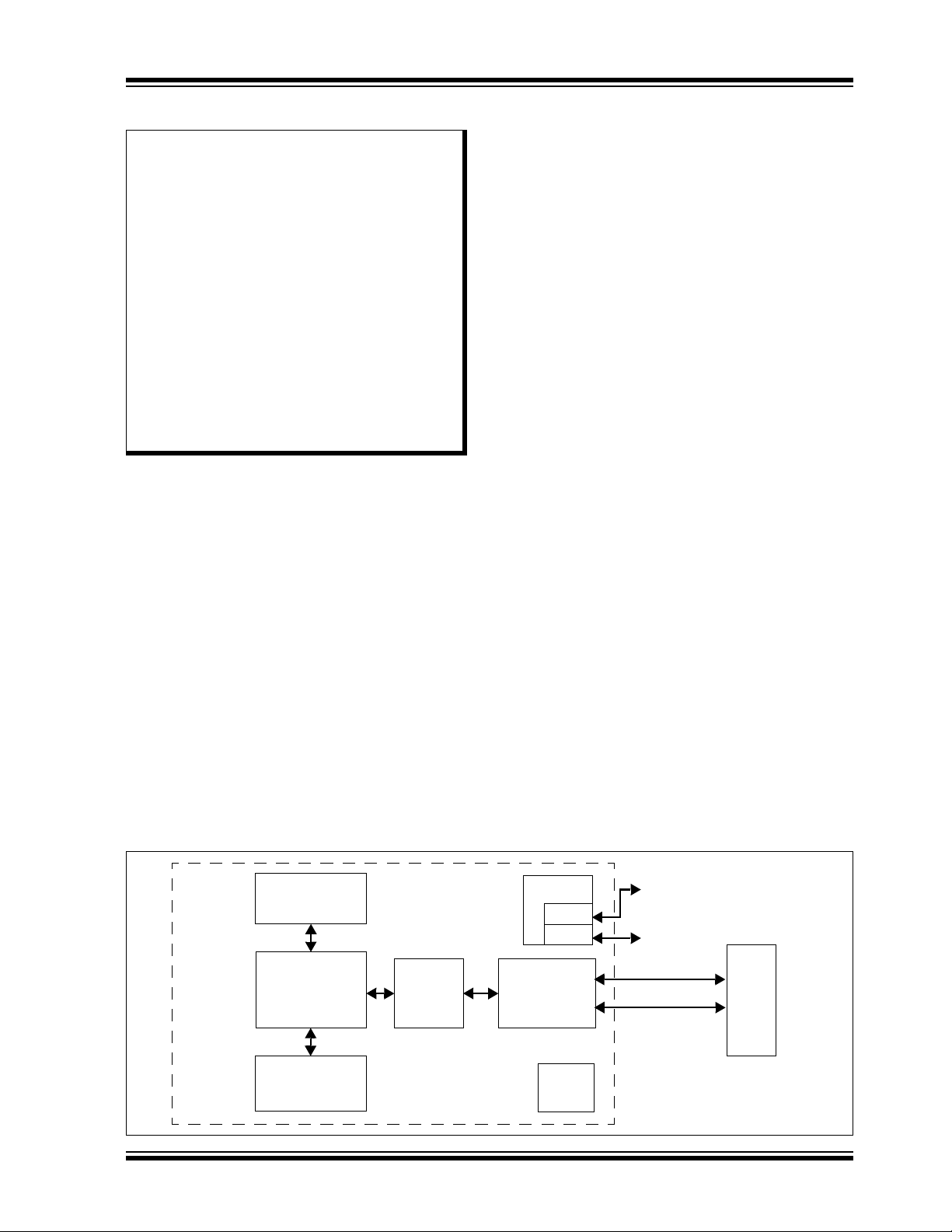

FIGURE 3-1: MIPS

®

M4K

®

BLOCK DIAGRAM

Note 1: This data sheet summarizes the features

of the PIC32MX3XX/4XX family of

devices. It is not intended to be a compre-

hensive reference source. To comple-

ment the information in this data sheet,

refer to Section 2. “CPU” (DS61113) of

the “PIC32 Family Reference Manual”,

which is available from the Microchip web

site (www.microchip.com/PIC32).

Resources for the MIPS32

®

M4K

®

Processor Core are available at:

www.mips.com/products/cores/

32-64-bit-cores/mips32-m4k/.

2: Some registers and associated bits

described in this section may not be avail-

able on all devices. Refer to Section 4.0

“Memory Organization” in this data

sheet for device-specific register and bit

information.

Dual Bus I/F

System

Coprocessor

MDU

FMT

TAP

EJTAG

Power

Mgmt.

Off-Chip

Debug I/F

Execution

Core

(RF/ALU/Shift)

Bus Matrix

Trace

Trace I/F

Bus Interface

CPU

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件