Datasheet 搜索 > 微控制器 > Microchip(微芯) > PIC32MX575F256H-80I/PT 数据手册 > PIC32MX575F256H-80I/PT 数据手册 117/240 页

器件3D模型

器件3D模型¥ 57.088

PIC32MX575F256H-80I/PT 数据手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

TQFP-64

描述:

MICROCHIP PIC32MX575F256H-80I/PT 微控制器, 32位, 人机接口, PIC32, 80 MHz, 256 KB, 64 KB, 64 引脚, TQFP

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P4P5P6P7P8P9P10P11P12P13P14P24Hot

原理图在P23P39P107P115P117P121P123P125P126P127P129P131

封装尺寸在P221

标记信息在P219P220

封装信息在P4P178P219P223P224P225P230P231P235P239

功能描述在P45P137

技术参数、封装参数在P178P182P183P184P185P186P188P207P208P209P217P235

电气规格在P36P122P163P217P235

导航目录

PIC32MX575F256H-80I/PT数据手册

Page:

of 240 Go

若手册格式错乱,请下载阅览PDF原文件

2009 Microchip Technology Inc. Preliminary DS61156B-page 117

PIC32MX5XX/6XX/7XX

10.0 DIRECT MEMORY ACCESS

(DMA) CONTROLLER

The PIC32MX Direct Memory Access (DMA) controller

is a bus master module useful for data transfers

between different devices without CPU intervention.

The source and destination of a DMA transfer can be

any of the memory mapped modules existent in the

PIC32MX (such as Peripheral Bus (PBUS) devices:

SPI, UART, I

2

C™, etc.) or memory itself.

Following are some of the key features of the DMA

controller module:

• Four Identical Channels, each featuring:

- Auto-Increment Source and Destination

Address Registers

- Source and Destination Pointers

- Memory to Memory and Memory to

Peripheral Transfers

• Automatic Word-Size Detection:

- Transfer Granularity, down to byte level

- Bytes need not be word-aligned at source

and destination

• Fixed Priority Channel Arbitration

• Flexible DMA Channel Operating modes:

- Manual (software) or automatic (interrupt)

DMA requests

- One-Shot or Auto-Repeat Block Transfer

modes

- Channel-to-channel chaining

• Flexible DMA Requests:

- A DMA request can be selected from any of

the peripheral interrupt sources

- Each channel can select any (appropriate)

observable interrupt as its DMA request

source

- A DMA transfer abort can be selected from

any of the peripheral interrupt sources

- Pattern (data) match transfer termination

• Multiple DMA Channel Status Interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half-full

- DMA transfer aborted due to an external

event

- Invalid DMA address generated

• DMA Debug Support Features:

- Most recent address accessed by a DMA

channel

- Most recent DMA channel to transfer data

• CRC Generation Module:

- CRC module can be assigned to any of the

available channels

- CRC module is highly configurable

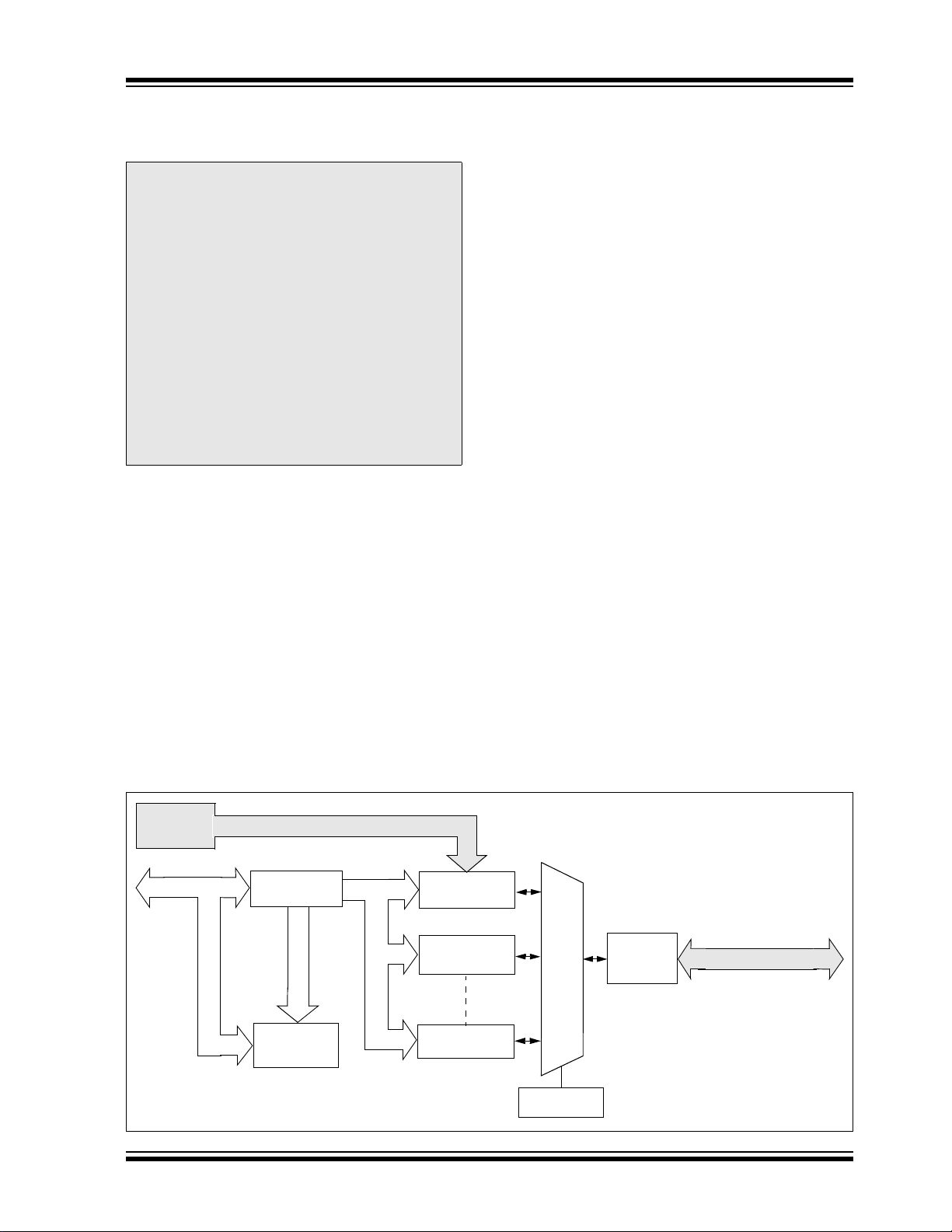

FIGURE 10-1: DMA BLOCK DIAGRAM

Note 1: This data sheet summarizes the features

of the PIC32MX5XX/6XX/7XX family of

devices. It is not intended to be a

comprehensive reference source. To

complement the information in this data

sheet, refer to

Section 31. “Direct

Memory Access (DMA) Controller”

(DS61117) in the “PIC32MX Family

Reference Manual”

, which is available

from the Microchip web site

(www.microchip.com/PIC32).

2: Some registers and associated bits

described in this section may not be avail-

able on all devices. Refer to

Section 4.0

“Memory Organization”

in this data

sheet for device-specific register and bit

information.

Peripheral Bus

Address Decoder

Channel 0 Control

Channel 1 Control

Channel n Control

Global Control

(DMACON)

Bus Interface

Channel Priority

Arbitration

S

E

L

S

E

L

Y

I

0

I

1

I

2

I

n

System IRQINT Controller

Device Bus + Bus Arbitration

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件