Datasheet 搜索 > 微控制器 > Microchip(微芯) > PIC32MX795F512H-80I/MR 数据手册 > PIC32MX795F512H-80I/MR 数据手册 431/441 页

器件3D模型

器件3D模型¥ 105.838

PIC32MX795F512H-80I/MR 数据手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

微控制器

封装:

QFN-64

描述:

MICROCHIP PIC32MX795F512H-80I/MR 微控制器, 32位, 图形接口, PIC32, 80 MHz, 512 KB, 128 KB, 64 引脚, QFN

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P38P423P428P431Hot

原理图在P25P41P69P95P101P111P157P167P171P172P177P181

封装尺寸在P403P430

标记信息在P401P402P430

封装信息在P2P3P4P352P401P403P404P405P407P409P410P411

功能描述在P47P221P279P323P327P333

技术参数、封装参数在P353P360P361P362P364P365P366P368P386P388P389P397

电气规格在P38P158P362P397P421P425P428P429P430P432

导航目录

PIC32MX795F512H-80I/MR数据手册

Page:

of 441 Go

若手册格式错乱,请下载阅览PDF原文件

2009-2016 Microchip Technology Inc. DS60001156J-page 431

PIC32MX5XX/6XX/7XX

Revision J (September 2016)

This revision includes typographical and formatting

updates throughout the data sheet text. In addition, all

SFR Register maps were moved from the Memory

chapter to their respective peripheral chapters.

All other major updates are referenced by their

respective section in Table B-7.

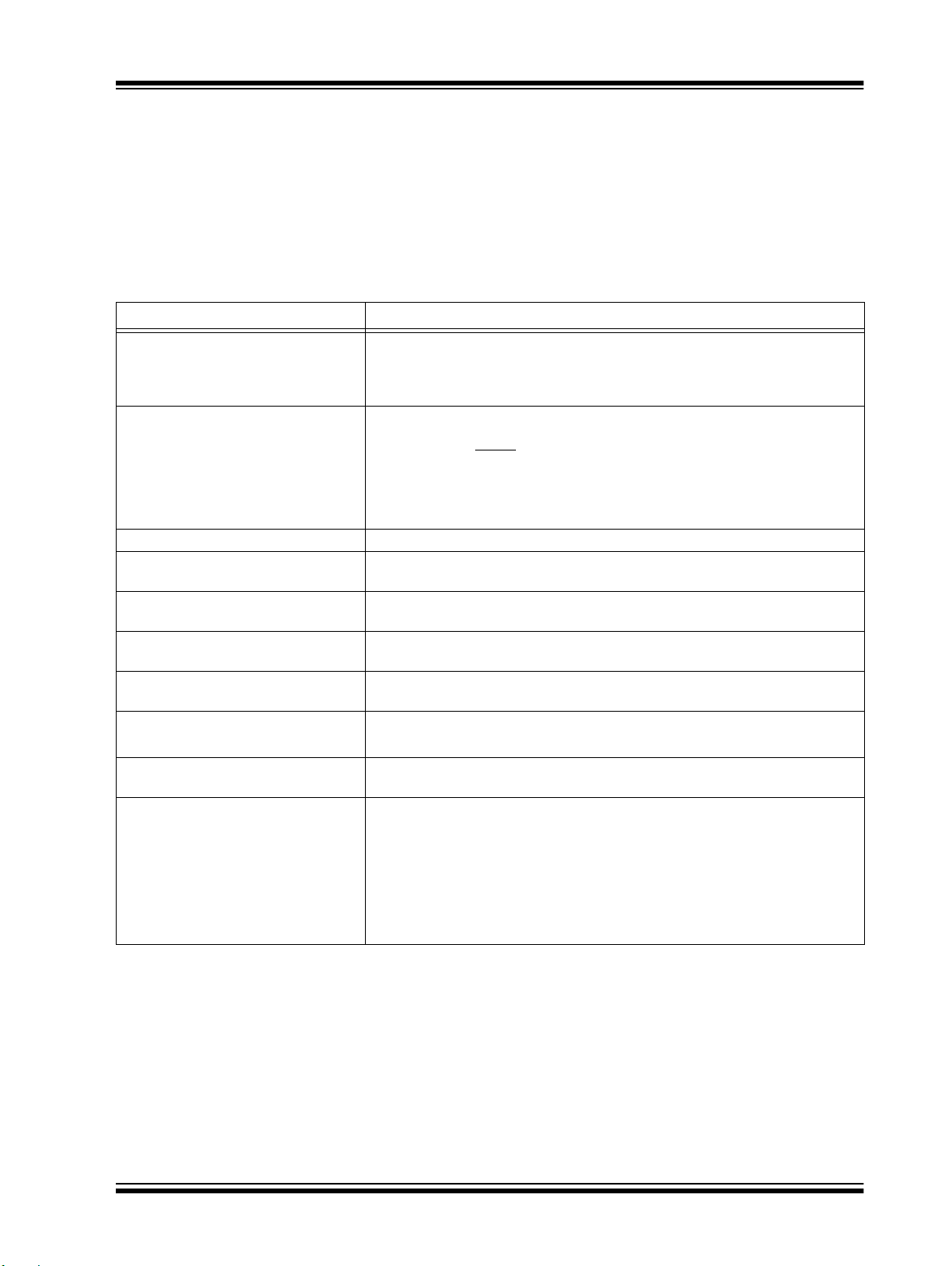

TABLE B-7: MAJOR SECTION UPDATES

Section Name Update Description

“32-bit Microcontrollers (up to 512

KB Flash and 128 KB SRAM) with

Graphics Interface, USB, CAN, and

Ethernet”

Updated Communication Interfaces for LIN support to 2.1.

Updated Qualification and Class B Support to AEC-Q100 REVH.

2.0 “Guidelines for Getting Started

with 32-bit MCUs”

The Recommended Minimum Connection diagram was updated (see

Figure 2-1).

The Example of MCLR

Pin Connections diagram was updated (see Figure 2-

2).

2.11 “EMI/EMC/EFT (IEC 61000-4-4 and IEC 61000-4-2) Suppression

Considerations”

was added.

4.0 “Memory Organization”

The SFR Memory Map was added (see Table 4-1).

7.0 “Interrupt Controller”

The UART interrupt sources were updated in the Interrupt IRQ, Vector, and

Bit location table (see Table 7-1).

8.0 “Oscillator Configuration”

Updated the bit value definitions for the TUN<5:0> bits in the OCSTUN

register (see Register 8-2).

15.0 “Watchdog Timer (WDT)”

The content in this chapter was relocated from the Special Features chapter

to its own chapter.

18.0 “Serial Peripheral Interface

(SPI)”

The register map tables were combined (see Table 18-1).

19.0 “Inter-Integrated Circuit (I

2

C)”

The register map tables were combined (see Table 19-1).

The PMADDR register was updated (see Register 21-3).

21.0 “Parallel Master Port (PMP)”

The bit value definitions for the ADRMUX<1:0> and CSF<1:0> bits in the

PMCON register were updated (see Register 21-1).

29.0 “Special Features”

Removed the duplicate bit value definition for ‘010’ in the DEVCFG2 register

(see Register 29-3).

Note 1 was added to the Programming, Debugging, and Trace Ports block

diagram (see Figure 29-2).

The DDPCON register was relocated (see Register 29-6).

The Device ID, Revision, and Configuration Summary was updated (see

Table 29-2).

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件