Datasheet 搜索 > 32位控制器 > Microchip(微芯) > PIC32MZ2048EFH144T-250I/PH 数据手册 > PIC32MZ2048EFH144T-250I/PH 数据手册 1/737 页

¥ 126.896

PIC32MZ2048EFH144T-250I/PH 数据手册 - Microchip(微芯)

制造商:

Microchip(微芯)

分类:

32位控制器

封装:

TQFP-144

描述:

RISC 252MHz 闪存:2MB

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P38P581P597P598P599P720Hot

典型应用电路图在P42

原理图在P15P44P71P109P115P169P173P247P283P287P288P293

封装尺寸在P679

焊盘布局在P40

标记信息在P677P678

封装信息在P612P677P679P680P681P682P683P684P686P688P691P692

功能描述在P43P61P523

技术参数、封装参数在P613P617P618P619P620P621P623P624P626P650P653P657

应用领域在P710

电气规格在P154P171P318P319P320P334P427P613P657P669P705P716

导航目录

PIC32MZ2048EFH144T-250I/PH数据手册

Page:

of 737 Go

若手册格式错乱,请下载阅览PDF原文件

2015-2016 Microchip Technology Inc. DS60001320D-page 1

PIC32MZ Embedded Connectivity

with Floating Point Unit (EF) Family

Operating Conditions

• 2.1V to 3.6V, -40ºC to +85ºC, DC to 252 MHz

• 2.1V to 3.6V, -40ºC to +125ºC, DC to 180 MHz

Core: 252 MHz (up to 415 DMIPS) M-Class

• 16 KB I-Cache, 4 KB D-Cache

• FPU for 32-bit and 64-bit floating point math

• MMU for optimum embedded OS execution

• microMIPS™ mode for up to 35% smaller code size

• DSP-enhanced core:

- Four 64-bit accumulators

- Single-cycle MAC, saturating, and fractional math

- IEEE 754-compliant

• Code-efficient (C and Assembly) architecture

Clock Management

• Programmable PLLs and oscillator clock sources

• Fail-Safe Clock Monitor (FSCM)

• Independent Watchdog Timers (WDT) and Deadman

Timer (DMT)

• Fast wake-up and start-up

Power Management

• Low-power modes (Sleep and Idle)

• Integrated Power-on Reset (POR) and Brown-out Reset

(BOR)

Memory Interfaces

• 50 MHz External Bus Interface (EBI)

• 50 MHz Serial Quad Interface (SQI)

Audio and Graphics Interfaces

• Graphics interfaces: EBI or PMP

• Audio data communication: I

2

S, LJ, and RJ

• Audio control interfaces: SPI and I

2

C

• Audio master clock: Fractional clock frequencies with USB

synchronization

High-Speed (HS) Communication Interfaces

(with Dedicated DMA)

• USB 2.0-compliant Hi-Speed On-The-Go (OTG) controller

• 10/100 Mbps Ethernet MAC with MII and RMII interface

Security Features

• Crypto Engine with RNG for data encryption/decryption and

authentication (AES, 3DES, SHA, MD5, and HMAC)

• Advanced memory protection:

- Peripheral and memory region access control

Direct Memory Access (DMA)

• Eight channels with automatic data size detection

• Programmable Cyclic Redundancy Check (CRC)

Advanced Analog Features

• 12-bit ADC module:

- 18 Msps with up to six Sample and Hold (S&H) circuits

(five dedicated and one shared)

- Up to 48 analog inputs

- Can operate during Sleep and Idle modes

- Multiple trigger sources

- Six Digital Comparators and six Digital Filters

• Two comparators with 32 programmable voltage

references

• Temperature sensor with ±2ºC accuracy

Communication Interfaces

• Two CAN modules (with dedicated DMA channels):

- 2.0B Active with DeviceNet™ addressing support

• Six UART modules (25 Mbps):

- Supports up to LIN 2.1 and IrDA

®

protocols

• Six 4-wire SPI modules (up to 50 MHz)

• SQI configurable as an additional SPI module (50 MHz)

•Five I

2

C modules (up to 1 Mbaud) with SMBus support

• Parallel Master Port (PMP)

• Peripheral Pin Select (PPS) to enable function remap

Timers/Output Compare/Input Capture

• Nine 16-bit or up to four 32-bit timers/counters

• Nine Output Compare (OC) modules

• Nine Input Capture (IC) modules

• Real-Time Clock and Calendar (RTCC) module

Input/Output

• 5V-tolerant pins with up to 32 mA source/sink

• Selectable open drain, pull-ups, pull-downs, and slew rate

controls

• External interrupts on all I/O pins

• PPS to enable function remap

Qualification and Class B Support

• AEC-Q100 REVH (Grade 1 -40ºC to +125ºC)

• Class B Safety Library, IEC 60730 (planned)

• Back-up internal oscillator

Debugger Development Support

• In-circuit and in-application programming

•4-wire MIPS

®

Enhanced JTAG interface

• Unlimited software and 12 complex breakpoints

• IEEE 1149.2-compatible (JTAG) boundary scan

• Non-intrusive hardware-based instruction trace

Software and Tools Support

• C/C++ compiler with native DSP/fractional and FPU support

•MPLAB

®

Harmony Integrated Software Framework

• TCP/IP, USB, Graphics, and mTouch™ middleware

• MFi, Android™, and Bluetooth

®

audio frameworks

• RTOS Kernels: Express Logic ThreadX, FreeRTOS™,

OPENRTOS

®

, Micriµm

®

µC/OS™, and SEGGER embOS

®

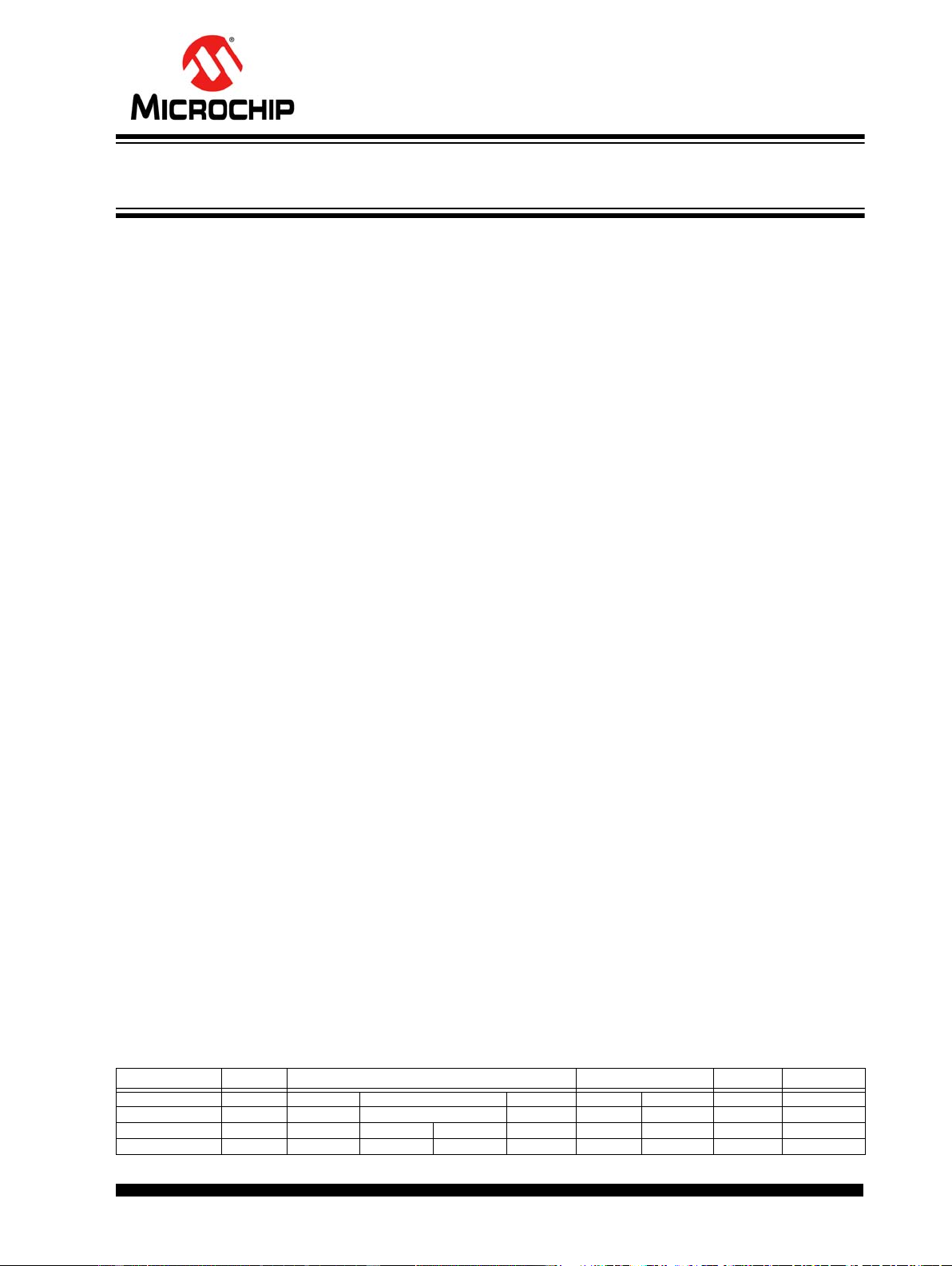

Packages

Type QFN TQFP

TFBGA

(1)

VTLA LQFP

Pin Count 64 64 100 144 100 144 124 144

I/O Pins (up to) 53 53 78 120 78 120 98 120

Contact/Lead Pitch 0.50 mm 0.50 mm 0.40 mm 0.50 mm 0.40 mm 0.65 mm 0.50 mm 0.50 mm 0.50 mm

Dimensions 9x9x0.9 mm 10x10x1 mm 12x12x1 mm 14x14x1 mm 16x16x1 mm 7x7x1.2 mm 7x7x1.2 mm 9x9x0.9 mm 20x20x1.40 mm

Note 1: Contact your local Microchip Sales Office for information on the availability of devices in the 100-pin and 144-pin TFBGA packages

32-bit MCUs (up to 2 MB Live-Update Flash and 512 KB SRAM) with FPU,

Audio and Graphics Interfaces, HS USB, Ethernet, and Advanced Analog

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件