Datasheet 搜索 > 射频接收器 > Silicon Labs(芯科) > SI4735-D60-GUR 数据手册 > SI4735-D60-GUR 数据手册 1/42 页

器件3D模型

器件3D模型¥ 3.315

SI4735-D60-GUR 数据手册 - Silicon Labs(芯科)

制造商:

Silicon Labs(芯科)

分类:

射频接收器

封装:

SSOP-24

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P1P29P40Hot

典型应用电路图在P18P19P26P40P42

原理图在P1P12P13P14P15P18P19P21P22P26P39P40

封装尺寸在P32P33

型号编码规则在P1P31

标记信息在P37P38

功能描述在P21P40

技术参数、封装参数在P5P17

应用领域在P1

电气规格在P5

导航目录

SI4735-D60-GUR数据手册

Page:

of 42 Go

若手册格式错乱,请下载阅览PDF原文件

Rev. 1.2 8/13 Copyright © 2013 by Silicon Laboratories Si473x-D60

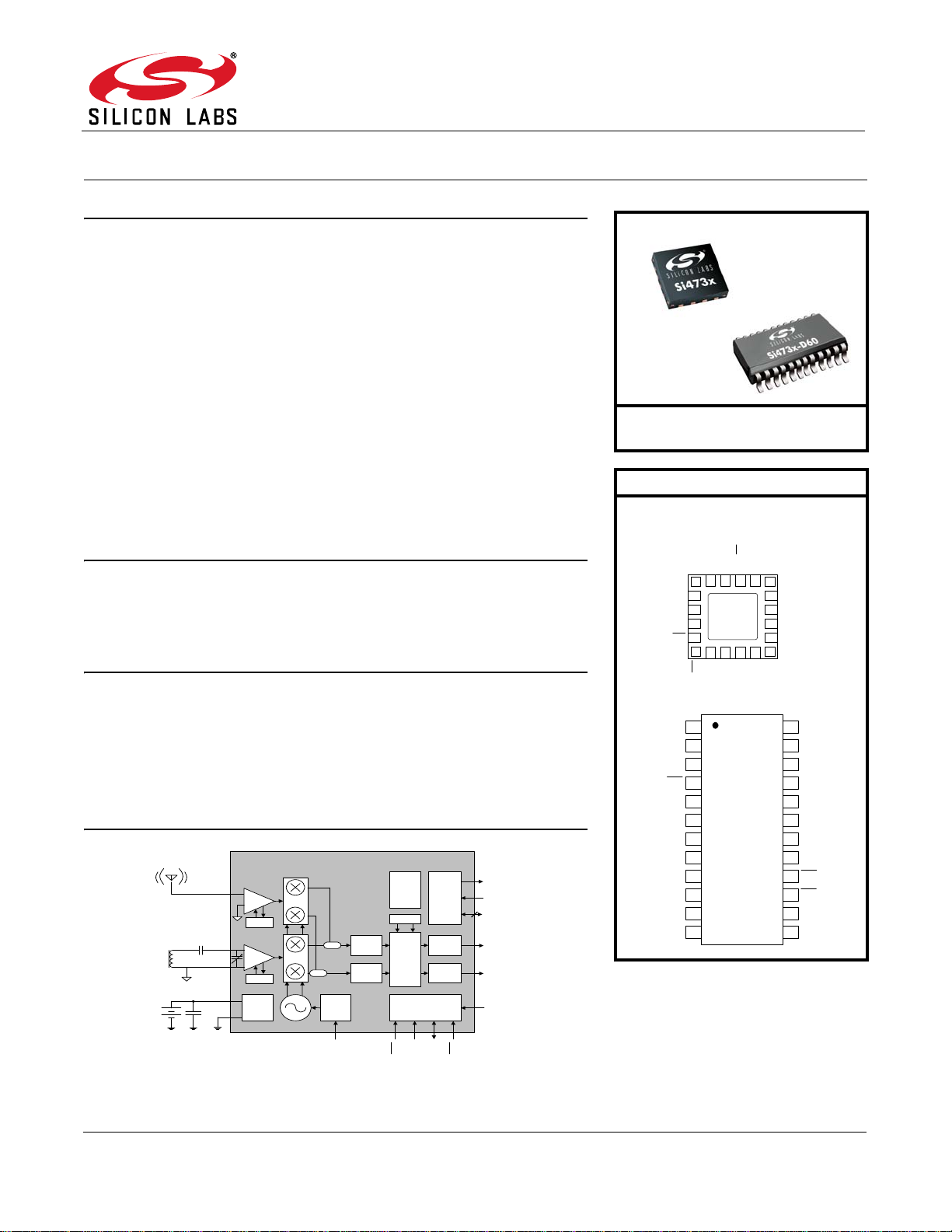

Si4730/31/34/35-D60

BROADCAST AM/FM/SW/LW RADIO RECEIVER

Features

Applications

Description

The Si473x-D60 digital CMOS AM/FM radio receiver IC integrates the complete

broadcast tuner and receiver function from antenna input to digital audio output.

The device leverages the Silicon Labs broadcast proven digital low-IF

architecture, enabling a cost-effective, digital audio platform for consumer

electronic applications with high TDMA noise immunity, superior radio

performance, and high fidelity audio power amplification.

Functional Block Diagram

Worldwide FM band support

(64–108 MHz)

Worldwide AM band support

(520–1710 kHz)

SW band support (Si4734/35)

(2.3–26.1 MHz)

LW band support (Si4734/35)

(153–279 kHz)

Excellent real-world performance

Integrated VCO

Advanced AM/FM seek tuning

Automatic frequency control (AFC)

Automatic gain control (AGC)

Digital FM stereo decoder

Programmable de-emphasis

Advanced Audio Processing

Seven selectable AM channel filters

AM/FM/SW/LW digital tuning

EN55020 compliant

No manual alignment necessary

Programmable reference clock

Adjustable soft mute control

RDS/RBDS processor (Si4731/35)

Digital audio out

2-wire and 3-wire control interface

Integrated LDO regulator

Wide range of ferrite loop sticks and

air loop antennas supported

QFN and SSOP packages

RoHS compliant

Table and portable radios

Mini/micro systems

CD/DVD and Blu-ray players

Stereo boom boxes

Modules for consumer electronics

Clock radios

Mini HiFi and docking stations

Entertainment systems

ADC

Si473x-D60

DSP

DAC

LOUT

ROUT

AFC

GPO/DCLK

LDO

VA

2.7~5.5 V (QFN)

2.0~5.5 V (SSOP)

RDS

(Si4731/

35)

AMI

VD

1.62 -3.6 V

SEN

CONTROL

INTERFACE

SCLK

LNA

AGC

LNA

AGC

GND

ADC

Mux

Mux

DAC

LOW-IF

SDIO

RST

DIGITAL

AUDIO

DFS

DOUT

RCLK

AM / LW

ANT

RFGND

FMI

FM / SW

ANT

+

This product, its features, and/or its

architecture is covered by one or more of

the following patents, as well as other

patents, pending and issued, both

foreign and domestic: 7,127,217;

7,272,373; 7,272,375; 7,321,324;

7,355,476; 7,426,376; 7,471,940;

7,339,503; 7,339,504.

Ordering Information:

See page 31.

Pin Assignments

Si473x-D60(SSOP)

Si473x-D60 (QFN)

GND

PAD

1

2

3

17181920

11

12

13

14

6

7 8 9

4

5

16

10

15

GPO2/[INT]

VD

DOUT

LOUT/[DFS]

ROUT/[DOUT]

GNDRST

NC

AMI

RCLK

SDIO

VA

FMI

RFGND

GPO3/[DCLK]

NC

GPO1

DFS

SCLK

SEN

LOUT/[DFS]

ROUT/[DOUT]

DBYP

VD

GPO2/[INT]

GPO3/[DCLK]

DOUT

DFS

1

2

3

4

5

6

7

8

9

10

11

12

GPO1

VA

SDIO

NC

NC

RCLK

SEN

FMI

RFGND

SCLK

GND

NC

NC

RST

GND

AMI

24

23

22

21

20

19

18

17

16

15

14

13

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件