Datasheet 搜索 > 电压电平转换器 > TI(德州仪器) > SN74AVC4T245PWT 数据手册 > SN74AVC4T245PWT 数据手册 1/36 页

器件3D模型

器件3D模型¥ 6.65

SN74AVC4T245PWT 数据手册 - TI(德州仪器)

制造商:

TI(德州仪器)

分类:

电压电平转换器

封装:

TSSOP-16

描述:

TEXAS INSTRUMENTS SN74AVC4T245PWT 芯片, 4位总线双收发器

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P3Hot

典型应用电路图在P1P12P14P15

原理图在P12

封装尺寸在P19P20P21P23P24

标记信息在P20P21

封装信息在P17P18P19P20P21P22P23P24

技术参数、封装参数在P4

应用领域在P1P36

电气规格在P6

导航目录

SN74AVC4T245PWT数据手册

Page:

of 36 Go

若手册格式错乱,请下载阅览PDF原文件

DIR

OE

A1

A2

B1

B2

Product

Folder

Sample &

Buy

Technical

Documents

Tools &

Software

Support &

Community

SN74AVC4T245

SCES576G –JUNE 2004–REVISED NOVEMBER 2014

SN74AVC4T245 Dual-Bit Bus Transceiver with Configurable Voltage Translation

and 3-State Outputs

1 Features 3 Description

This 4-bit noninverting bus transceiver uses two

1

• Control Inputs V

IH

/V

IL

Levels Are Referenced to

separate configurable power-supply rails. The A port

V

CCA

Voltage

is designed to track V

CCA

. V

CCA

accepts any supply

• Fully Configurable Dual-Rail Design Allows Each

voltage from 1.2 V to 3.6 V. The B port is designed to

Port to Operate Over the Full 1.2-V to 3.6-V

track V

CCB

. V

CCB

accepts any supply voltage from

Power-Supply Range

1.2 V to 3.6 V. The SN74AVC4T245 is optimized to

operate with V

CCA

/V

CCB

set at 1.4 V to 3.6 V. It is

• I/Os Are 4.6-V Tolerant

operational with V

CCA

/V

CCB

as low as 1.2 V. This

• I

off

Supports Partial Power-Down-Mode Operation

allows for universal low-voltage bidirectional

• Maximum Data Rates

translation between any of the 1.2-V, 1.5-V, 1.8-V,

2.5-V, and 3.3-V voltage nodes.

– 380 Mbps (1.8-V to 3.3-V Translation)

– 200 Mbps (< 1.8-V to 3.3-V Translation)

The SN74AVC4T245 device is designed for

asynchronous communication between two data

– 200 Mbps (Translate to 2.5 V or 1.8 V)

buses. The logic levels of the direction-control (DIR)

– 150 Mbps (Translate to 1.5 V)

input and the output-enable (OE) input activate either

– 100 Mbps (Translate to 1.2 V)

the B-port outputs or the A-port outputs or place both

output ports into the high-impedance mode. The

• Latch-Up Performance Exceeds 100 mA Per

device transmits data from the A bus to the B bus

JESD 78, Class II

when the B-port outputs are activated, and from the B

• ESD Protection Exceeds JESD 22

bus to the A bus when the A-port outputs are

– 8000-V Human-Body Model (A114-A)

activated. The input circuitry on both A and B ports is

always active and must have a logic HIGH or LOW

– 150-V Machine Model (A115-A)

level applied to prevent excess I

CC

and I

CCZ

.

– 1000-V Charged-Device Model (C101)

The SN74AVC4T245 device is designed so that the

2 Applications

control pins (1DIR, 2DIR, 1OE, and 2OE) are

supplied by V

CCA

.

• Personal Electronics

This device is fully specified for partial-power-down

• Industrial

applications using I

off

. The I

off

circuitry disables the

• Enterprise

outputs, preventing damaging current backflow

• Telecom

through the device when it is powered down.

The V

CC

isolation feature ensures that if either V

CC

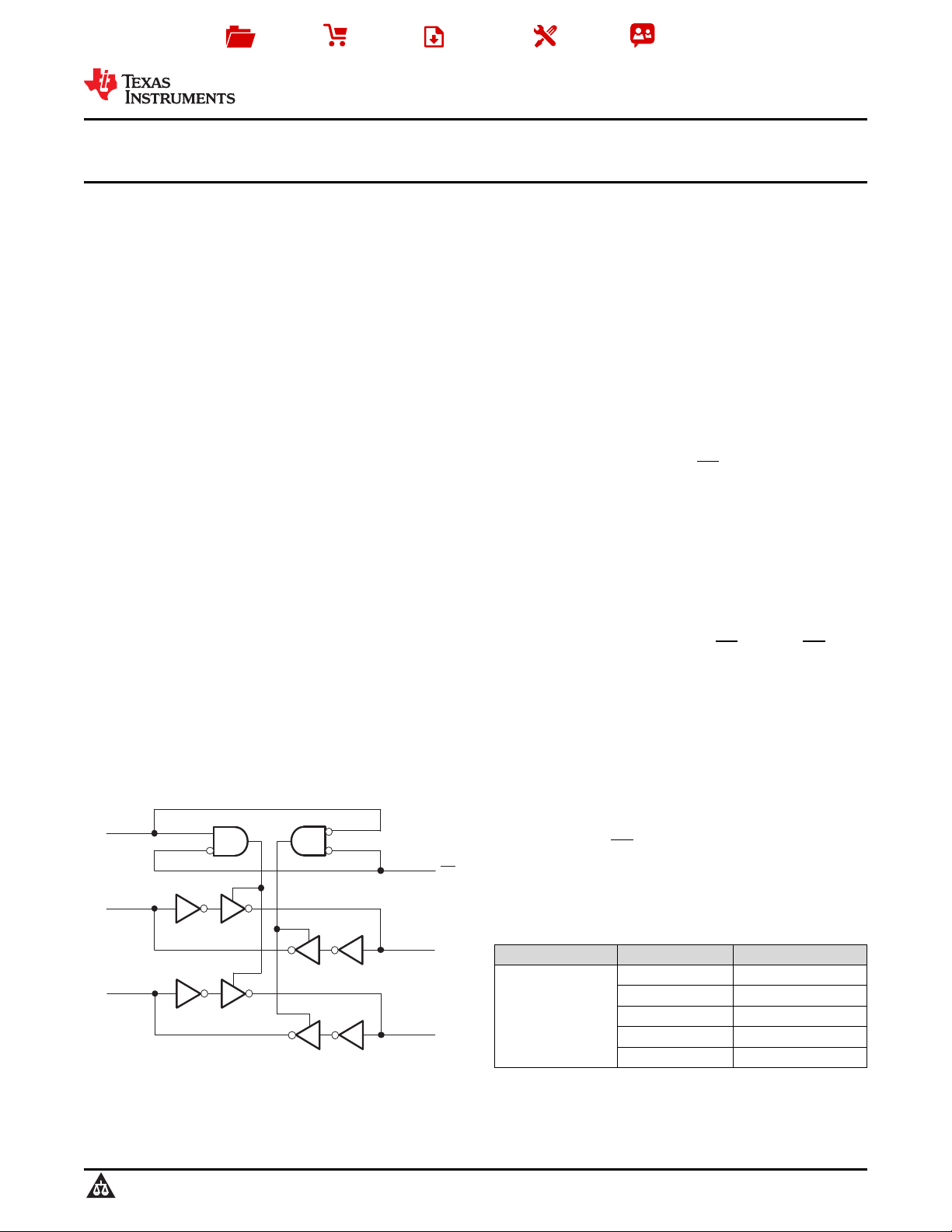

Logic Diagram (Positive Logic)

input is at GND, then both ports are in the high-

for 1/2 of SN74AVC4T245

impedance state.

To ensure the high-impedance state during power up

or power down, OE should be tied to V

CC

through a

pullup resistor; the minimum value of the resistor is

determined by the current-sinking capability of the

driver.

Device Information

(1)

PART NUMBER PACKAGE BODY SIZE (NOM)

SOIC (16) 9.90 mm x 3.91 mm

TVSOP (16) 3.60 mm x 4.40 mm

SN74AVC4T245 TSSOP (16) 5.00 mm x 4.40 mm

VQFN (16) 4.00 mm x 3.50 mm

UQFN (16) 2.60 mm x 1.80 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件