Datasheet 搜索 > Sonix(松翰) > SN8P26042AKG 数据手册 > SN8P26042AKG 数据手册 48/101 页

¥ 0

SN8P26042AKG 数据手册 - Sonix(松翰)

制造商:

Sonix(松翰)

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

导航目录

SN8P26042AKG数据手册

Page:

of 101 Go

若手册格式错乱,请下载阅览PDF原文件

SN8P2604A

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 48 Version 0.3

4

4

4

SYSTEM CLOCK

4.1 OVERVIEW

The micro-controller is a dual clock system. There are high-speed clock and low-speed clock. The high-speed clock is

generated from the external oscillator circuit. The low-speed clock is generated from on-chip low-speed RC oscillator

circuit (ILRC 16KHz @3V, 32KHz @5V).

Both the high-speed clock and the low-speed clock can be system clock (Fosc). The system clock in slow mode is

divided by 4 to be the instruction cycle (Fcpu).

) Normal Mode (High Clock): Fcpu = Fhosc / N, N = 1 ~ 8, Select N by Fcpu code option.

) Slow Mode (Low Clock): Fcpu = Flosc/4.

SONIX provides a “Noise Filter” controlled by code option. In high noisy situation, the noise filter can isolate noise

outside and protect system works well. The minimum Fcpu of high clock is limited at Fhosc/4 when noise filter enable.

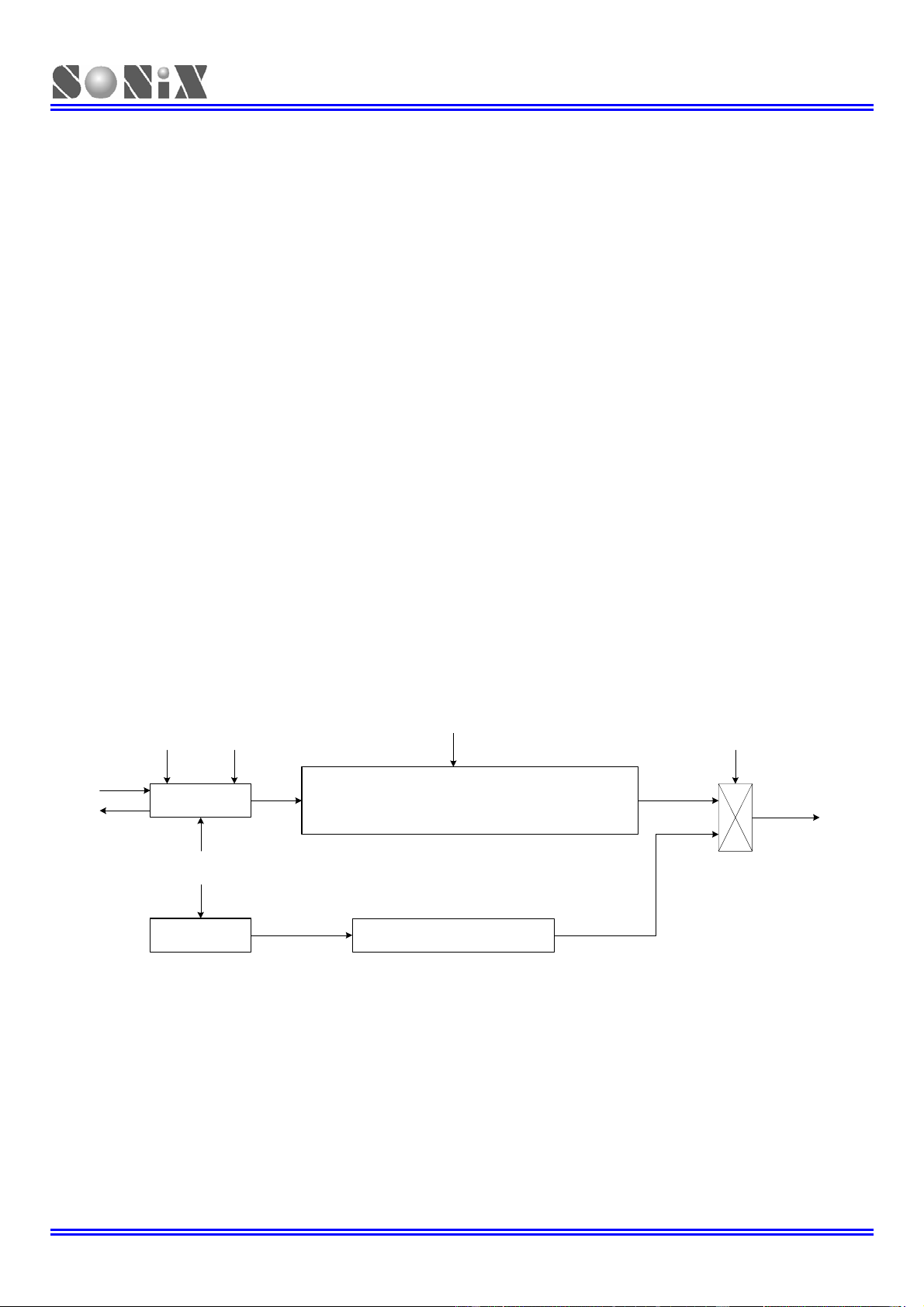

4.2 CLOCK BLOCK DIAGRAM

Fhosc.

Fcpu = Fhosc/1 ~ Fhosc/8, Noise Filter Disable.

Fcpu = Fhosc/4 ~ Fhosc/8, Noise Filter Enable.

Flosc. Fcpu = Flosc/4

CPUM[1:0]

XIN

XOUT

STPHX HOSC

Fcpu Code Option

Fosc

Fosc

CLKMD

Fcpu

z HOSC: High_Clk code option.

z Fhosc: External high-speed clock.

z Flosc: Internal low-speed RC clock (about 16KHz@3V, 32KHz@5V).

z Fosc: System clock source.

z Fcpu: Instruction cycle.

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件