Datasheet 搜索 > ST Microelectronics(意法半导体) > STM32F417IGH6W 数据手册 > STM32F417IGH6W 数据手册 106/203 页

¥ 49.872

STM32F417IGH6W 数据手册 - ST Microelectronics(意法半导体)

制造商:

ST Microelectronics(意法半导体)

封装:

UFBGA-201

描述:

ARM Cortex-M4 168MHz 闪存:1MB RAM:192KB

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P41P42P43P44P45P46P47P48P49P50P51P52Hot

典型应用电路图在P103P104P137

封装尺寸在P165P166P167P168P169P170P171P172P173P174P175P176

型号编码规则在P186

技术参数、封装参数在P78P113

电气规格在P76P77P78P79P80P81P82P83P84P85P86P87

导航目录

STM32F417IGH6W数据手册

Page:

of 203 Go

若手册格式错乱,请下载阅览PDF原文件

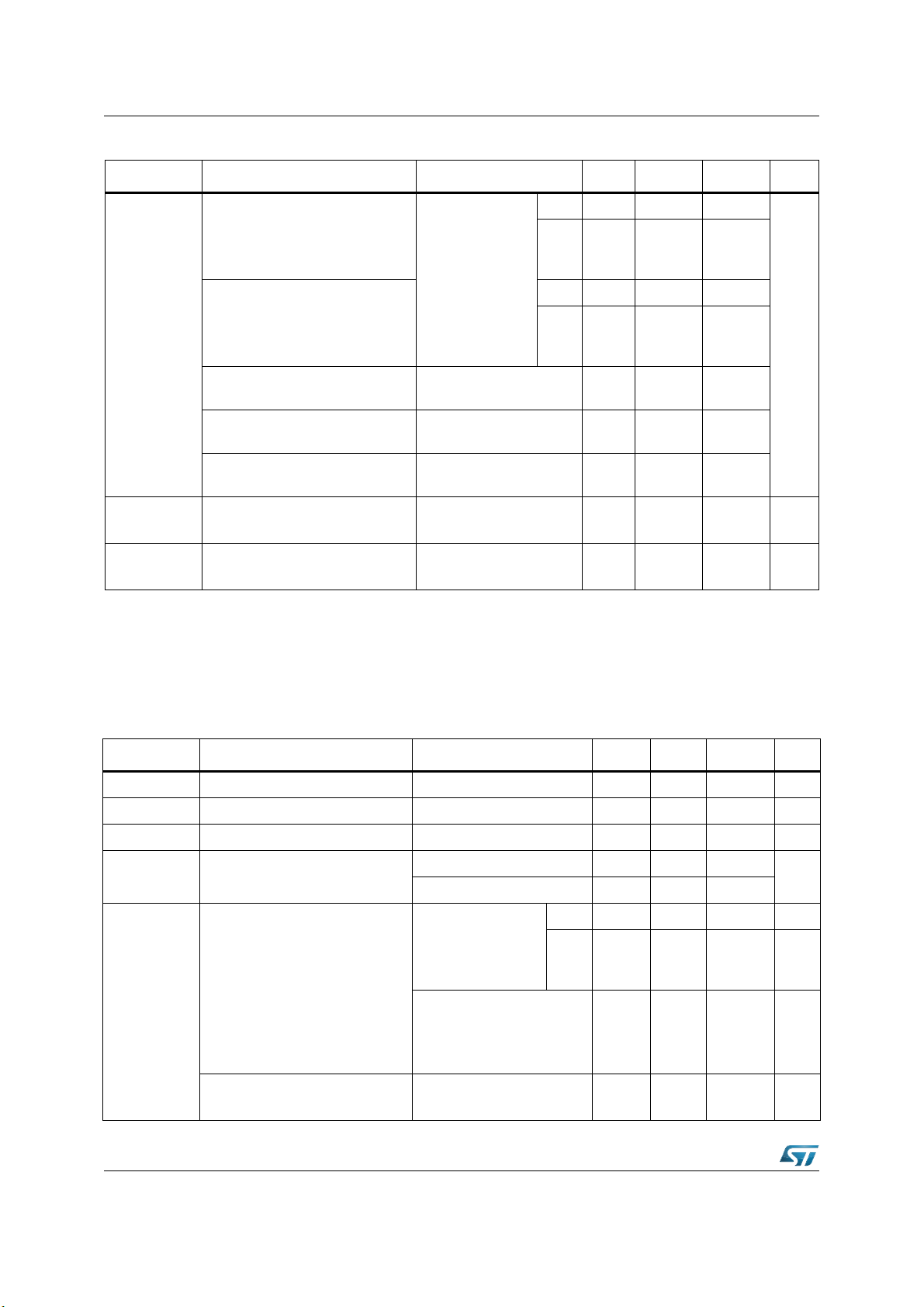

Electrical characteristics STM32F415xx, STM32F417xx

106/203 DocID022063 Rev 6

Jitter

(3)

Cycle-to-cycle jitter

System clock

120 MHz

RMS - 25 -

ps

peak

to

peak

- ±150 -

Period Jitter

RMS - 15 -

peak

to

peak

- ±200 -

Main clock output (MCO) for

RMII Ethernet

Cycle to cycle at 50 MHz

on 1000 samples

-32 -

Main clock output (MCO) for MII

Ethernet

Cycle to cycle at 25 MHz

on 1000 samples

-40 -

Bit Time CAN jitter

Cycle to cycle at 1 MHz

on 1000 samples

- 330 -

I

DD(PLL)

(4)

PLL power consumption on VDD

VCO freq = 100 MHz

VCO freq = 432 MHz

0.15

0.45

-

0.40

0.75

mA

I

DDA(PLL)

(4)

PLL power consumption on

VDDA

VCO freq = 100 MHz

VCO freq = 432 MHz

0.30

0.55

-

0.40

0.85

mA

1. Take care of using the appropriate division factor M to obtain the specified PLL input clock values. The M factor is shared

between PLL and PLLI2S.

2. Guaranteed by design.

3. The use of 2 PLLs in parallel could degraded the Jitter up to +30%.

4. Guaranteed by characterization.

Table 36. Main PLL characteristics (continued)

Symbol Parameter Conditions Min Typ Max Unit

Table 37. PLLI2S (audio PLL) characteristics

Symbol Parameter Conditions Min Typ Max Unit

f

PLLI2S_IN

PLLI2S input clock

(1)

-0.95

(2)

12.10MHz

f

PLLI2S_OUT

PLLI2S multiplier output clock - - - 216 MHz

f

VCO_OUT

PLLI2S VCO output - 100 - 432 MHz

t

LOCK

PLLI2S lock time

VCO freq = 100 MHz 75 - 200

µs

VCO freq = 432 MHz 100 - 300

Jitter

(3)

Master I

2

S clock jitter

Cycle to cycle at

12.288 MHz on

48KHz period,

N=432, R=5

RMS - 90 -

peak

to

peak

- ±280 - ps

Average frequency of

12.288 MHz

N = 432, R = 5

on 1000 samples

-90 -ps

WS I

2

S clock jitter

Cycle to cycle at 48 KHz

on 1000 samples

-400 - ps

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件