Datasheet 搜索 > ST Microelectronics(意法半导体) > STM32F417IGH6W 数据手册 > STM32F417IGH6W 数据手册 164/203 页

¥ 49.872

STM32F417IGH6W 数据手册 - ST Microelectronics(意法半导体)

制造商:

ST Microelectronics(意法半导体)

封装:

UFBGA-201

描述:

ARM Cortex-M4 168MHz 闪存:1MB RAM:192KB

Pictures:

3D模型

符号图

焊盘图

引脚图

产品图

页面导航:

引脚图在P41P42P43P44P45P46P47P48P49P50P51P52Hot

典型应用电路图在P103P104P137

封装尺寸在P165P166P167P168P169P170P171P172P173P174P175P176

型号编码规则在P186

技术参数、封装参数在P78P113

电气规格在P76P77P78P79P80P81P82P83P84P85P86P87

导航目录

STM32F417IGH6W数据手册

Page:

of 203 Go

若手册格式错乱,请下载阅览PDF原文件

Electrical characteristics STM32F415xx, STM32F417xx

164/203 DocID022063 Rev 6

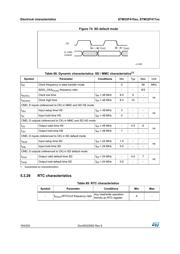

Figure 74. SD default mode

5.3.29 RTC characteristics

CK

D, CMD

(output)

t

OVD

t

OHD

ai14888

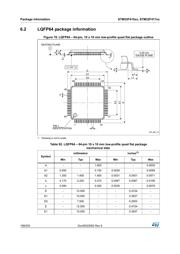

Table 88. Dynamic characteristics: SD / MMC characteristics

(1)

Symbol Parameter Conditions Min Typ Max Unit

f

PP

Clock frequency in data transfer mode 0 48 MHz

SDIO_CK/f

PCLK2

frequency ratio - - 8/3 -

t

W(CKL)

Clock low time f

PP

= 48 MHz 8.5 9 -

ns

t

W(CKH)

Clock high time f

PP

= 48 MHz 8.3 10 -

CMD, D inputs (referenced to CK) in MMC and SD HS mode

t

ISU

Input setup time HS f

PP

= 48 MHz 3 - -

ns

t

IH

Input hold time HS f

PP

= 48 MHz 0 - -

CMD, D outputs (referenced to CK) in MMC and SD HS mode

t

OV

Output valid time HS f

PP

= 48 MHz - 4.5 6

ns

t

OH

Output hold time HS f

PP

= 48 MHz 1 - -

CMD, D inputs (referenced to CK) in SD default mode

t

ISUD

Input setup time SD f

PP

= 24 MHz 1.5 - -

ns

t

IHD

Input hold time SD f

PP

= 24 MHz 0.5 - -

CMD, D outputs (referenced to CK) in SD default mode

t

OVD

Output valid default time SD f

PP

= 24 MHz - 4.5 7

ns

t

OHD

Output hold default time SD f

PP

= 24 MHz 0.5 - -

1. Guaranteed by characterization.

Table 89. RTC characteristics

Symbol Parameter Conditions Min Max

-f

PCLK1

/RTCCLK

frequency ratio

Any read/write operation

from/to an RTC register

4-

器件 Datasheet 文档搜索

AiEMA 数据库涵盖高达 72,405,303 个元件的数据手册,每天更新 5,000 多个 PDF 文件